封装信息

| CAD 模型: | View CAD Model |

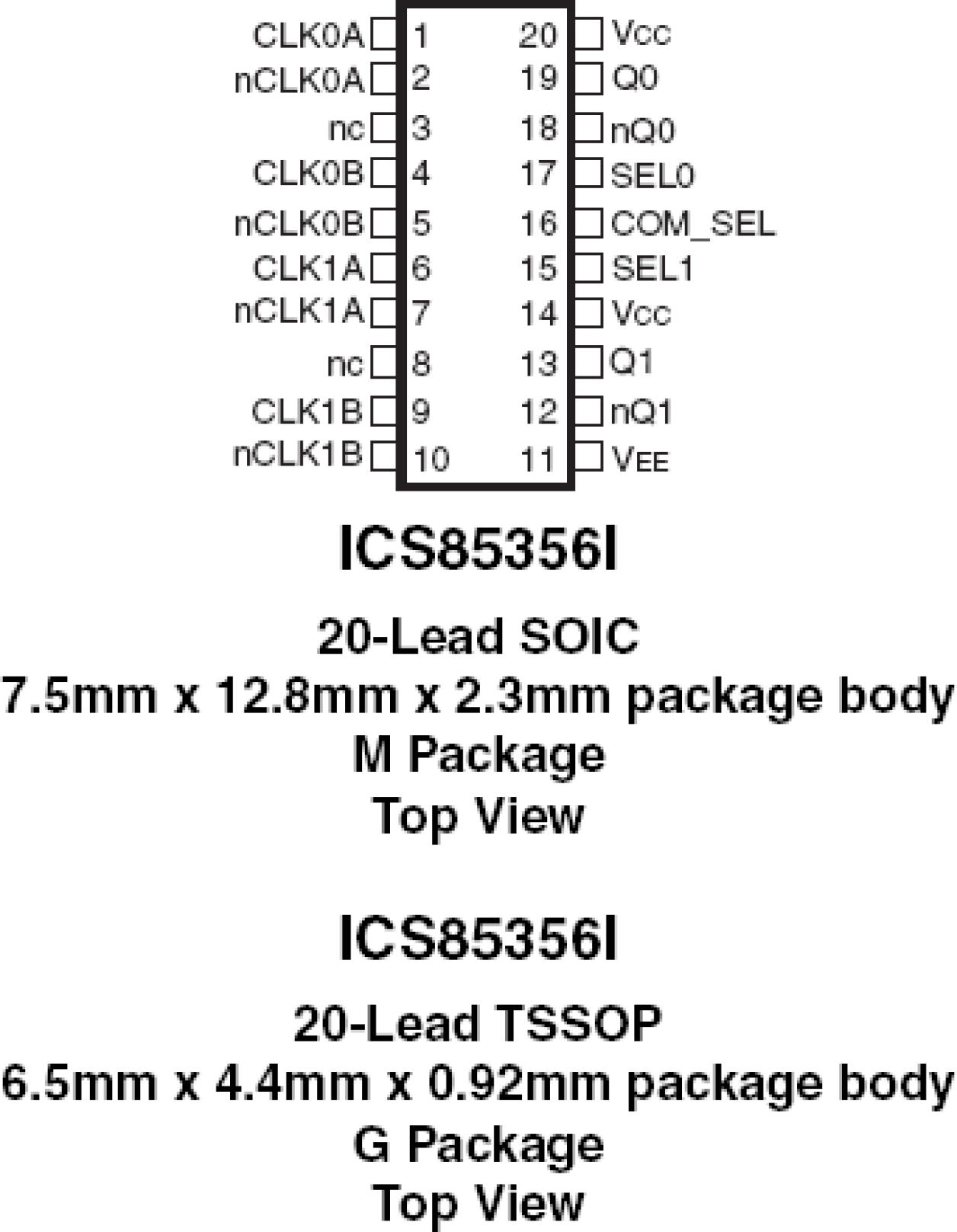

| Pkg. Type: | SOIC |

| Pkg. Code: | PSG20 |

| Lead Count (#): | 20 |

| Pkg. Dimensions (mm): | 12.8 x 7.6 x 2.34 |

| Pitch (mm): | 1.27 |

环境和出口类别

| Moisture Sensitivity Level (MSL) | 1 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

产品属性

| Lead Count (#) | 20 |

| Carrier Type | Reel |

| Moisture Sensitivity Level (MSL) | 1 |

| Qty. per Reel (#) | 1000 |

| Qty. per Carrier (#) | 0 |

| Package Area (mm²) | 97.3 |

| Pitch (mm) | 1.27 |

| Pkg. Dimensions (mm) | 12.8 x 7.6 x 2.34 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range (°C) | -40 to 85°C |

| Core Voltage (V) | 3.3 |

| Function | Multiplexer |

| Input Freq (MHz) | 900 |

| Input Type | HCSL, HSTL, LVDS, LVPECL, SSTL |

| Inputs (#) | 4 |

| Length (mm) | 12.8 |

| MOQ | 1000 |

| Output Banks (#) | 2 |

| Output Freq Range (MHz) | 900 |

| Output Skew (ps) | 150 |

| Output Type | LVPECL |

| Output Voltage (V) | 3.3 |

| Outputs (#) | 2 |

| Pkg. Type | SOIC |

| Product Category | Clock Multiplexers |

| Reel Size (in) | 13 |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Tape & Reel | Yes |

| Thickness (mm) | 2.34 |

| Width (mm) | 7.6 |

有关 85356I 的资源

描述

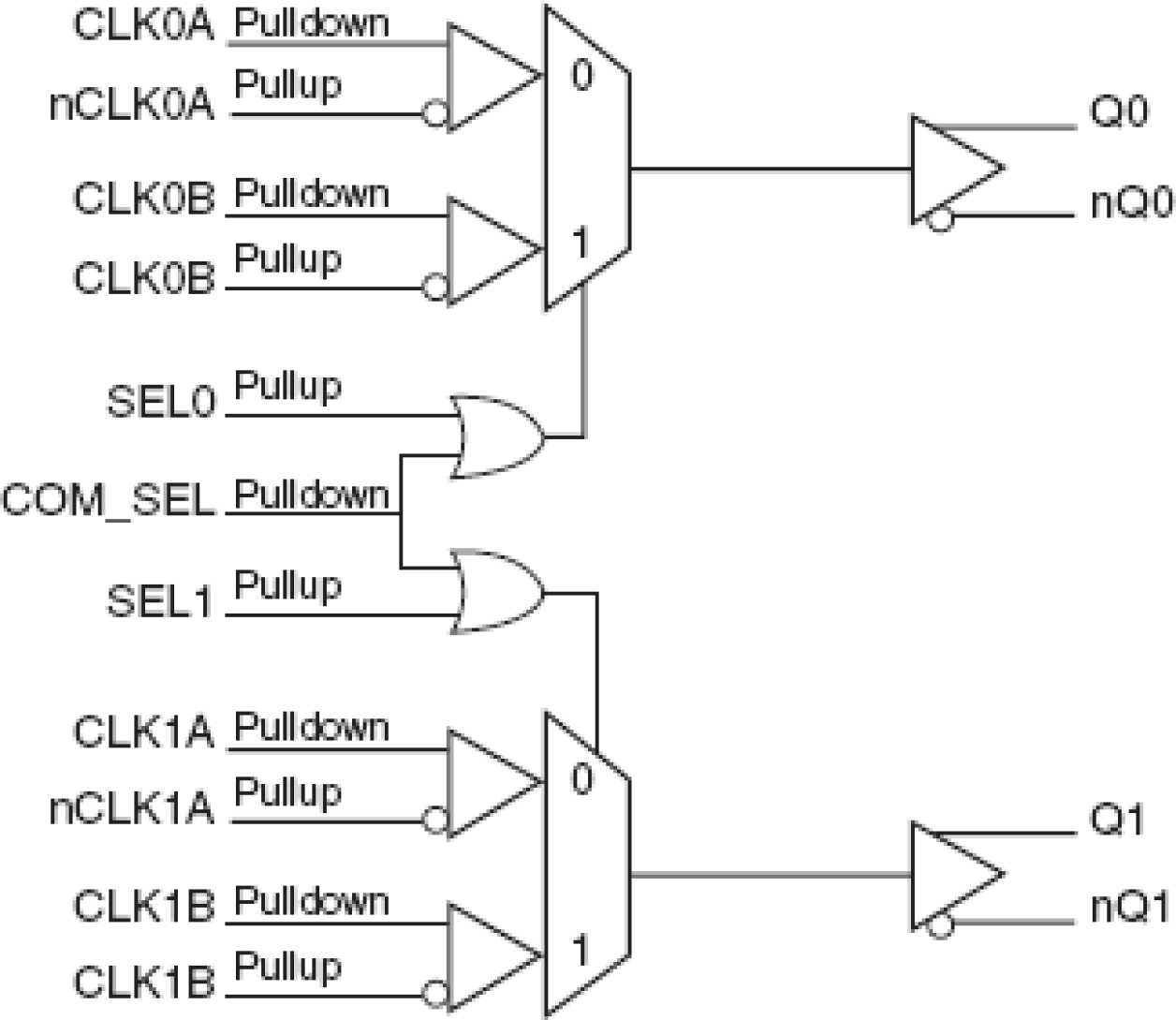

The 85356I is a dual 2:1 Differential-to-LVPECL Multiplexer. The device has both common select and individual select inputs. When COM_SEL is logic High, the CLKxx input pairs will be passed to the output. When COM_SEL is logic Low, the output is determined by the setting of the SEL0 pin for channel 0 and the SEL1 pin for Channel 1. The differential input has a common mode range that can accept most differential input types such as LVPECL, LVDS, LVHSTL, SSTL, and HCSL. The 85356I can therefore be used as a differential translator to translate almost any differential input type to LVPECL. It can also be used in ECL mode by setting VCC = 0V and VEE to -3.0V to - 3.8V. The 85356I adds negligible jitter to the input clock and can operate at high frequencies in excess of 900MHz thus making it ideal for use in demanding applications such as SONET, Fibre Channel, 1 Gigabit/10 Gigabit Ethernet.