警告信息

请登录或注册账户以查看此安全文档。

特性

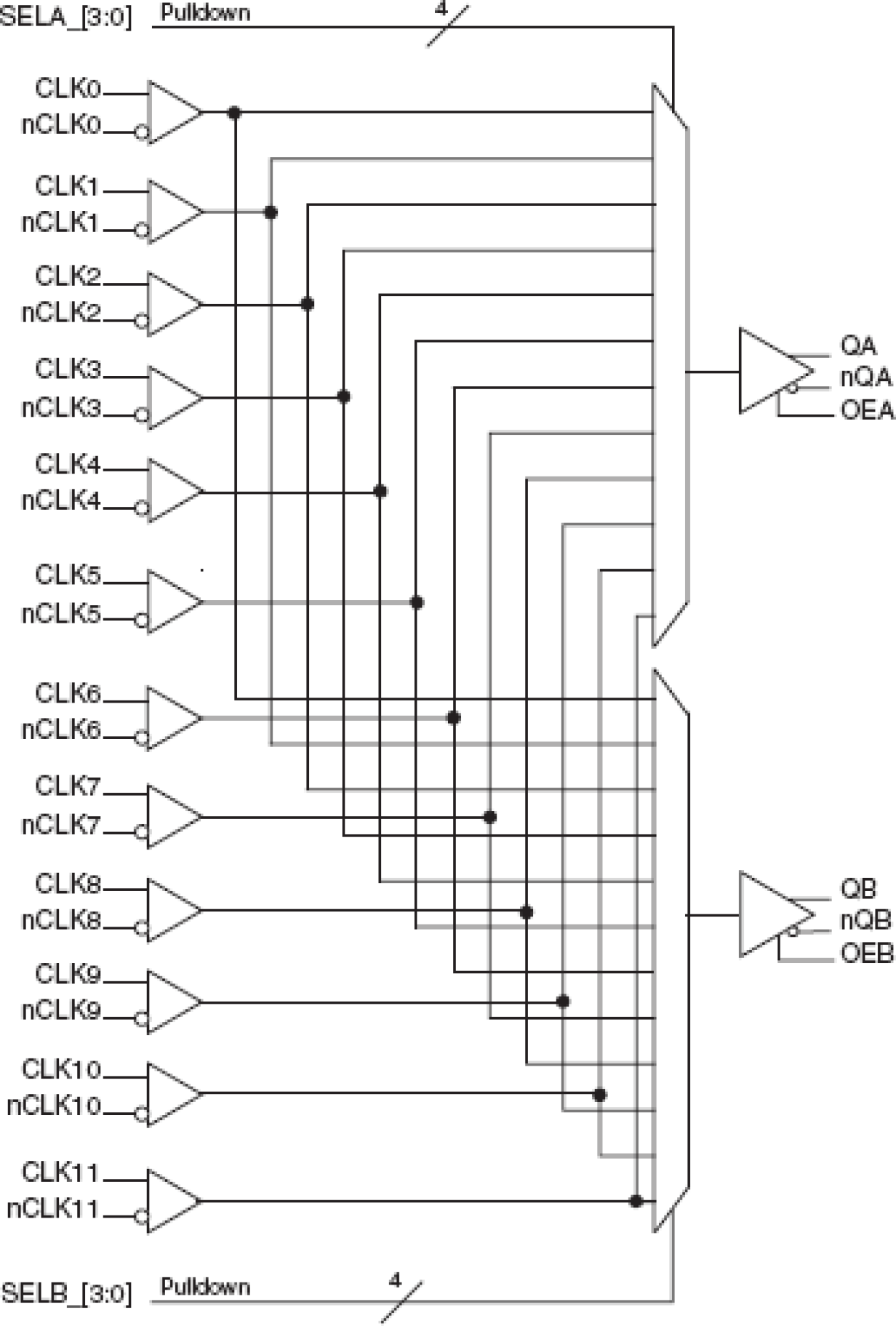

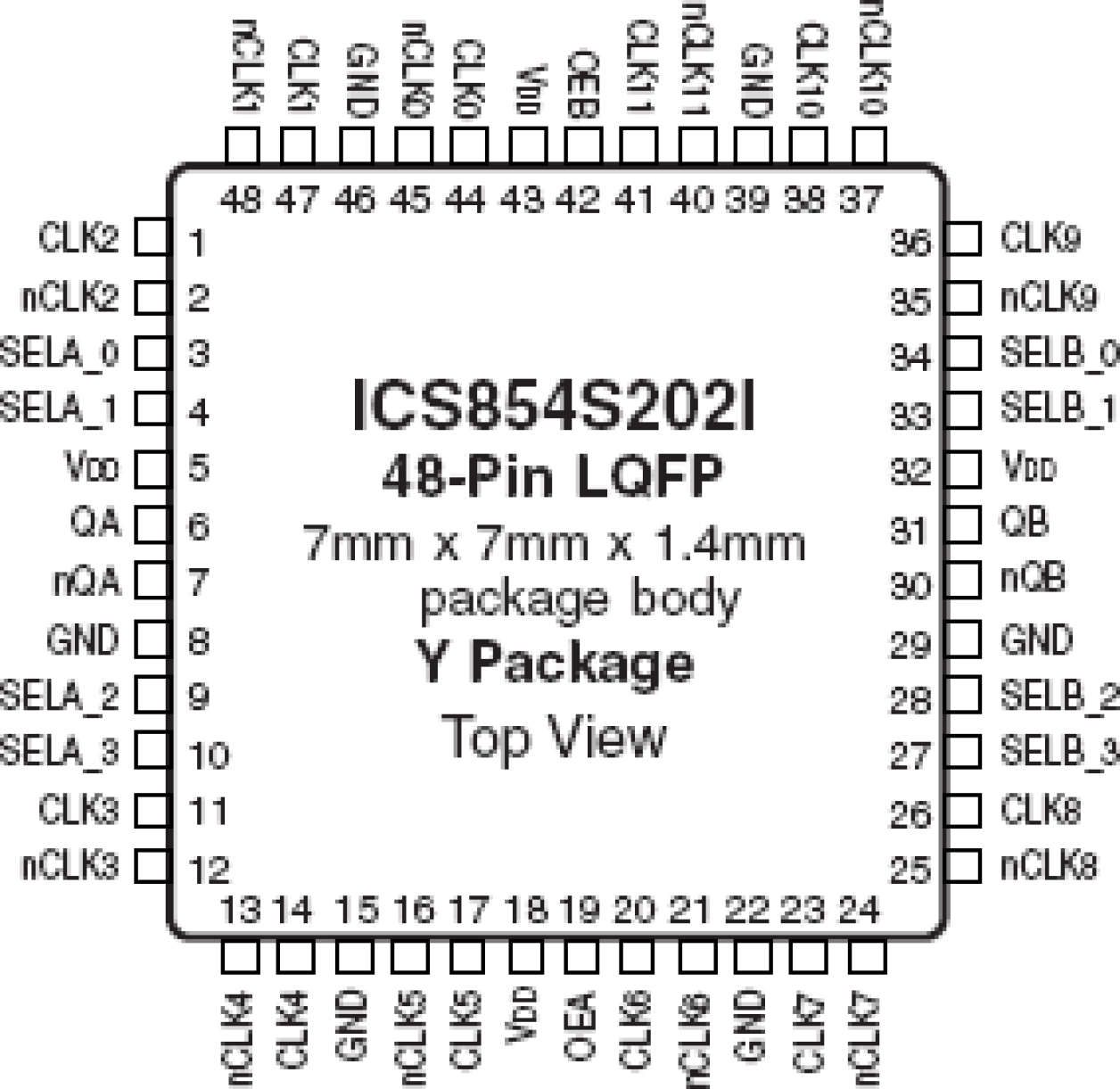

- Two differential 3.3V LVDS clock outputs

- Twelve selectable differential clock inputs

- CLKx, nCLKx pairs can accept the following differential input levels: LVPECL, LVDS, HSTL, SSTL, HCSL

- Maximum output frequency: >3GHz

- Propagation delay: 660ps (typical)

- Input skew: TBD

- Output skew: 25ps (typical)

- Part-to-part skew: TBD

- Additive phase jitter, RMS: 0.16ps (typical)

- Full 3.3V operating supply mode

- -40°C to 85°C ambient operating temperature

- Available in lead-free (RoHS 6) package

描述

The 854S202I is a 12:2 Differential-to-LVDS Clock Multiplexer which can operate >3GHz. The 854S202I has 12 selectable differential clock inputs, any of which can be independently routed to either of the two LVDS outputs. The CLKx, nCLKx input pairs can accept LVPECL, LVDS, CML or SSTL levels. The fully differential architecture and low propagation delay make it ideal for use in clock distribution circuits.

当前筛选条件