封装信息

| CAD 模型: | View CAD Model |

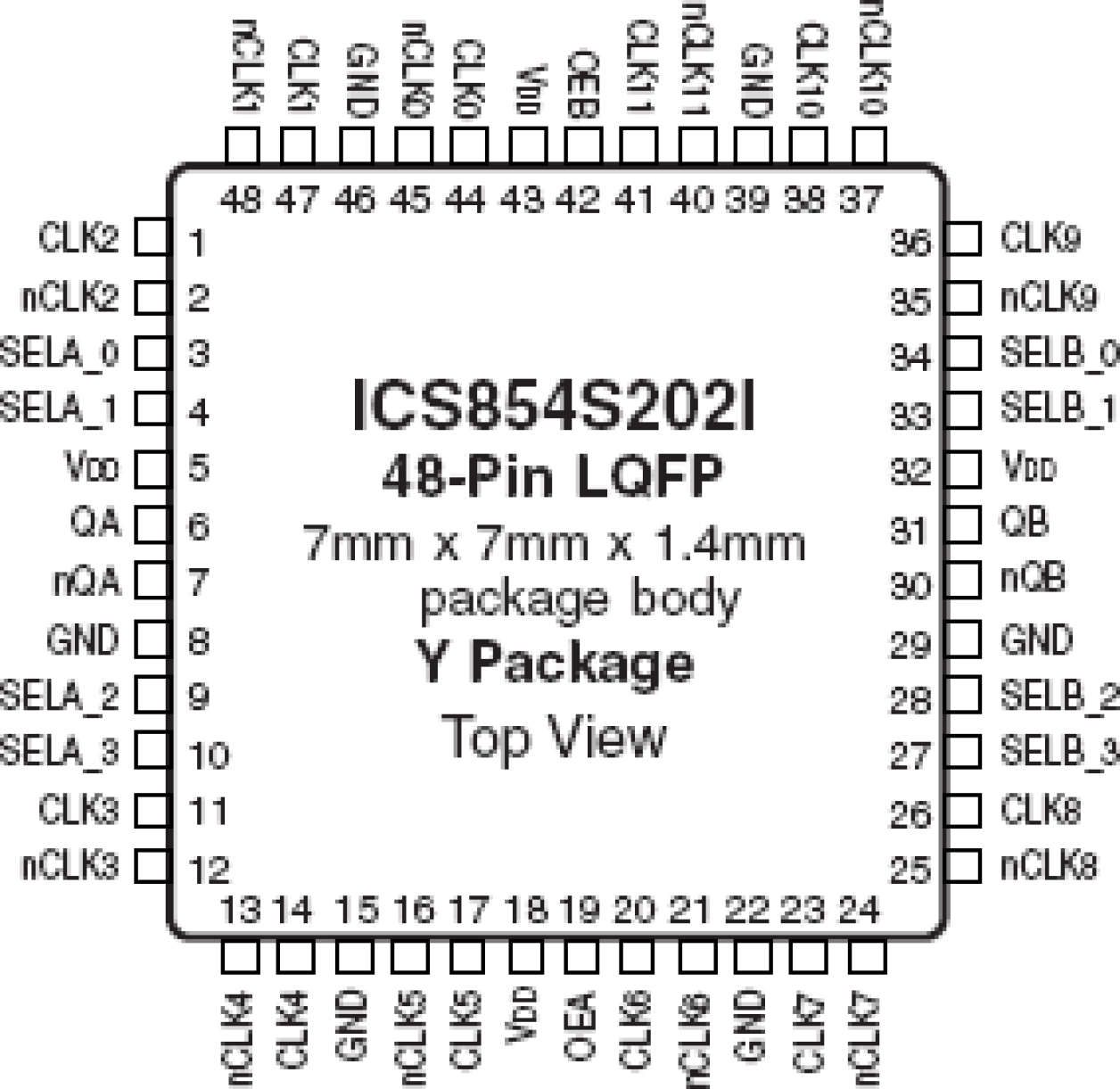

| Pkg. Type: | TQFP |

| Pkg. Code: | PRG48 |

| Lead Count (#): | 48 |

| Pkg. Dimensions (mm): | 7.0 x 7.0 x 1.4 |

| Pitch (mm): | 0.5 |

环境和出口类别

| Moisture Sensitivity Level (MSL) | 3 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

产品属性

| Lead Count (#) | 48 |

| Carrier Type | Tray |

| Moisture Sensitivity Level (MSL) | 3 |

| Qty. per Reel (#) | 0 |

| Qty. per Carrier (#) | 250 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range (°C) | -40 to 85°C |

| Additive Phase Jitter Typ RMS (fs) | 160 |

| Additive Phase Jitter Typ RMS (ps) | 0.16 |

| Core Voltage (V) | 3.3 |

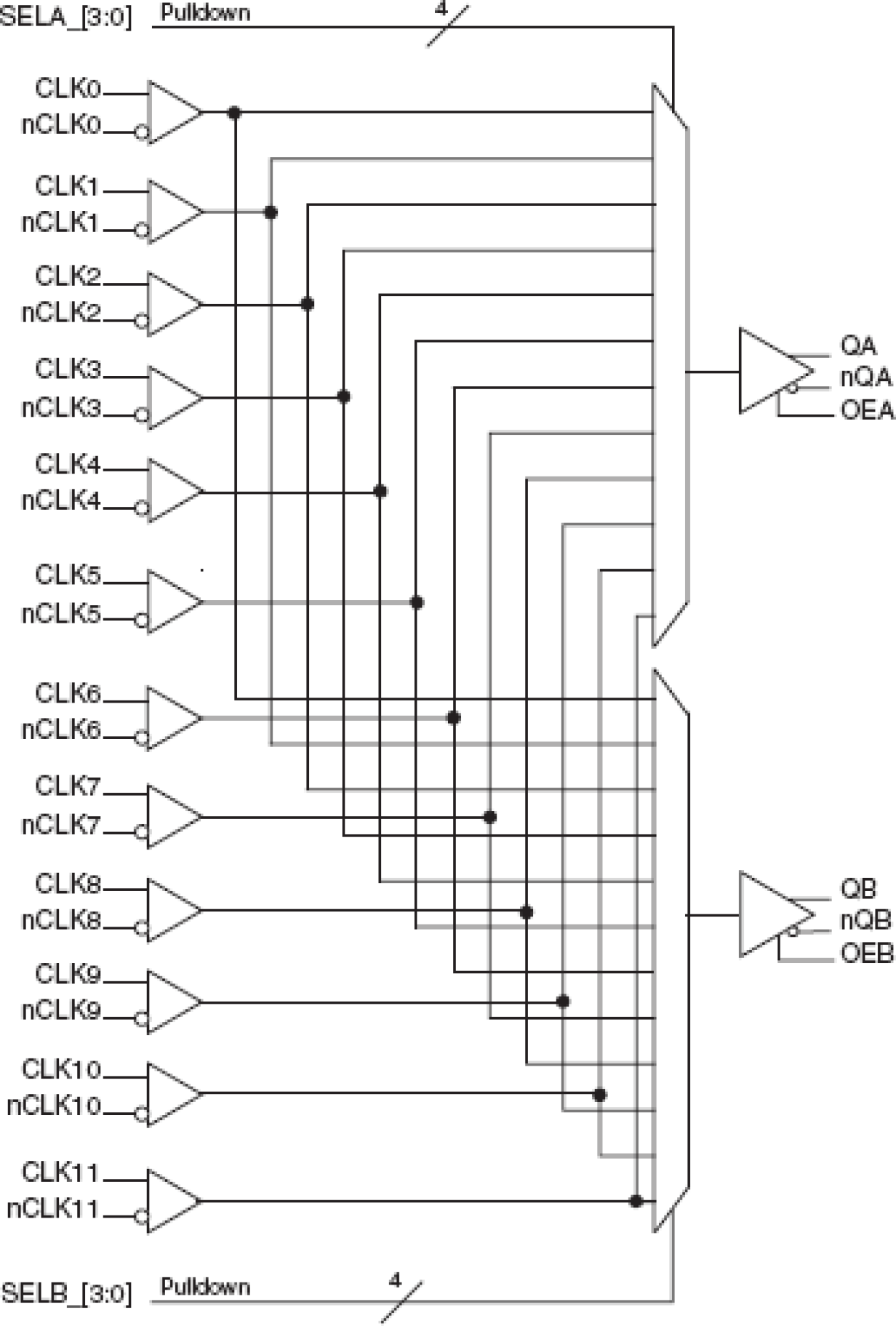

| Function | Multiplexer |

| Input Freq (MHz) | 3000 |

| Input Type | HCSL, HSTL, LVDS, LVPECL, SSTL |

| Inputs (#) | 12 |

| Length (mm) | 7 |

| MOQ | 2000 |

| Output Banks (#) | 2 |

| Output Freq Range (MHz) | 3000 |

| Output Skew (ps) | 25 |

| Output Type | LVDS |

| Output Voltage (V) | 3.3 |

| Outputs (#) | 2 |

| Package Area (mm²) | 49 |

| Pitch (mm) | 0.5 |

| Pkg. Dimensions (mm) | 7.0 x 7.0 x 1.4 |

| Pkg. Type | TQFP |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Tape & Reel | No |

| Thickness (mm) | 1.4 |

| Width (mm) | 7 |

| 已发布 | No |

有关 854S202I 的资源

描述

The 854S202I is a 12:2 Differential-to-LVDS Clock Multiplexer which can operate >3GHz. The 854S202I has 12 selectable differential clock inputs, any of which can be independently routed to either of the two LVDS outputs. The CLKx, nCLKx input pairs can accept LVPECL, LVDS, CML or SSTL levels. The fully differential architecture and low propagation delay make it ideal for use in clock distribution circuits.