封装信息

| CAD 模型: | View CAD Model |

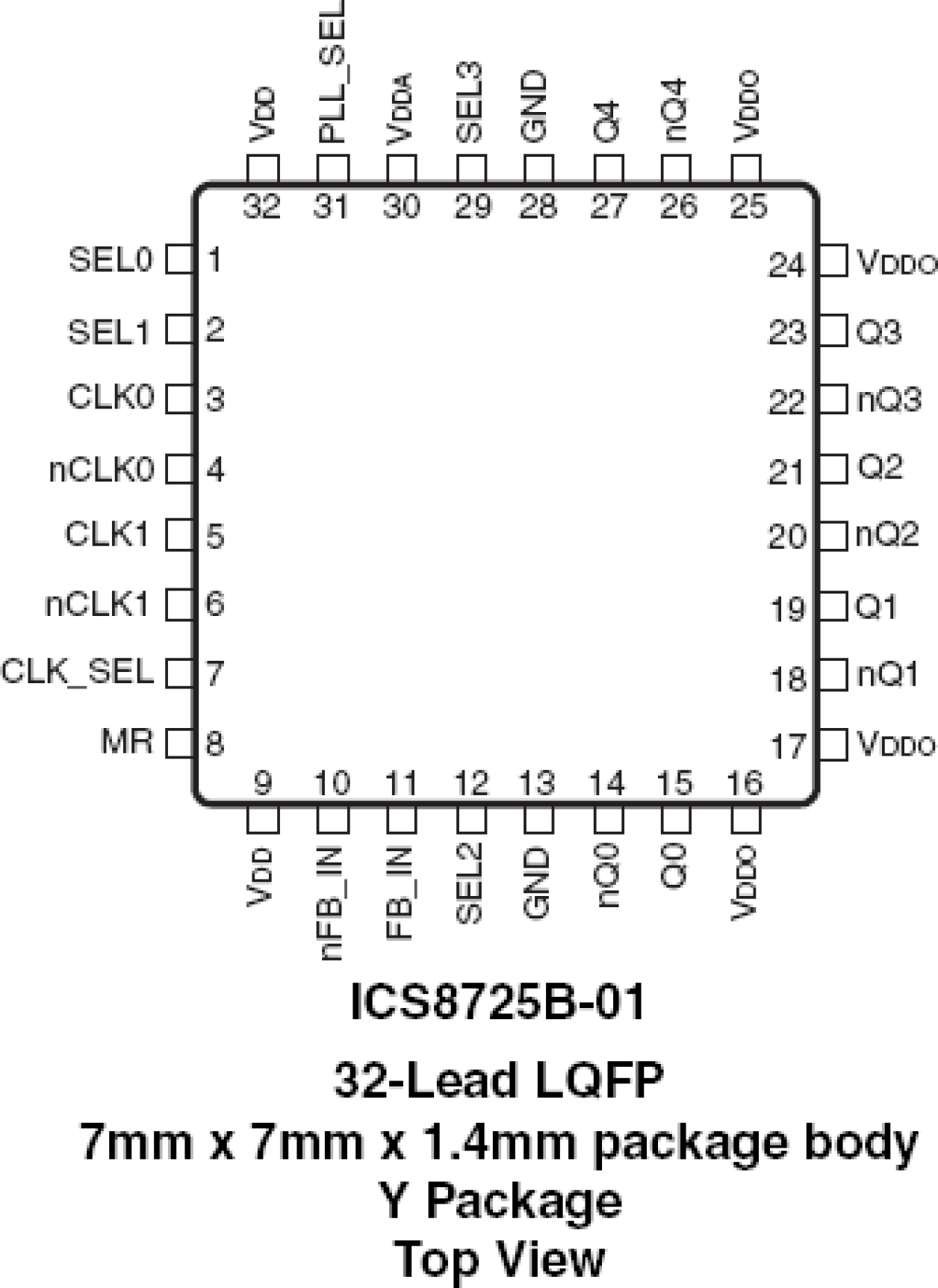

| Pkg. Type: | TQFP |

| Pkg. Code: | PRG32 |

| Lead Count (#): | 32 |

| Pkg. Dimensions (mm): | 7.0 x 7.0 x 1.4 |

| Pitch (mm): | 0.8 |

环境和出口类别

| Moisture Sensitivity Level (MSL) | 3 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

产品属性

| Lead Count (#) | 32 |

| Carrier Type | Tray |

| Moisture Sensitivity Level (MSL) | 3 |

| Qty. per Reel (#) | 0 |

| Qty. per Carrier (#) | 250 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range (°C) | 0 to 70°C |

| Advanced Features | Feedback Input |

| C-C Jitter Max P-P (ps) | 25 |

| Core Voltage (V) | 3.3 |

| Feedback Input | Yes |

| Input Freq (MHz) | 31.25 - 700 |

| Input Type | HCSL, HSTL, LVDS, LVPECL, SSTL |

| Inputs (#) | 2 |

| Length (mm) | 7 |

| MOQ | 250 |

| Output Banks (#) | 1 |

| Output Freq Range (MHz) | 31.25 - 700 |

| Output Skew (ps) | 45 |

| Output Type | HSTL |

| Output Voltage (V) | 1.8 |

| Outputs (#) | 5 |

| Package Area (mm²) | 49 |

| Phase Jitter Max RMS (ps) | 50 |

| Pitch (mm) | 0.8 |

| Pkg. Dimensions (mm) | 7.0 x 7.0 x 1.4 |

| Pkg. Type | TQFP |

| Product Category | Zero Delay Buffers |

| Prog. Clock | No |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Tape & Reel | No |

| Thickness (mm) | 1.4 |

| Width (mm) | 7 |

有关 8725B-01 的资源

描述

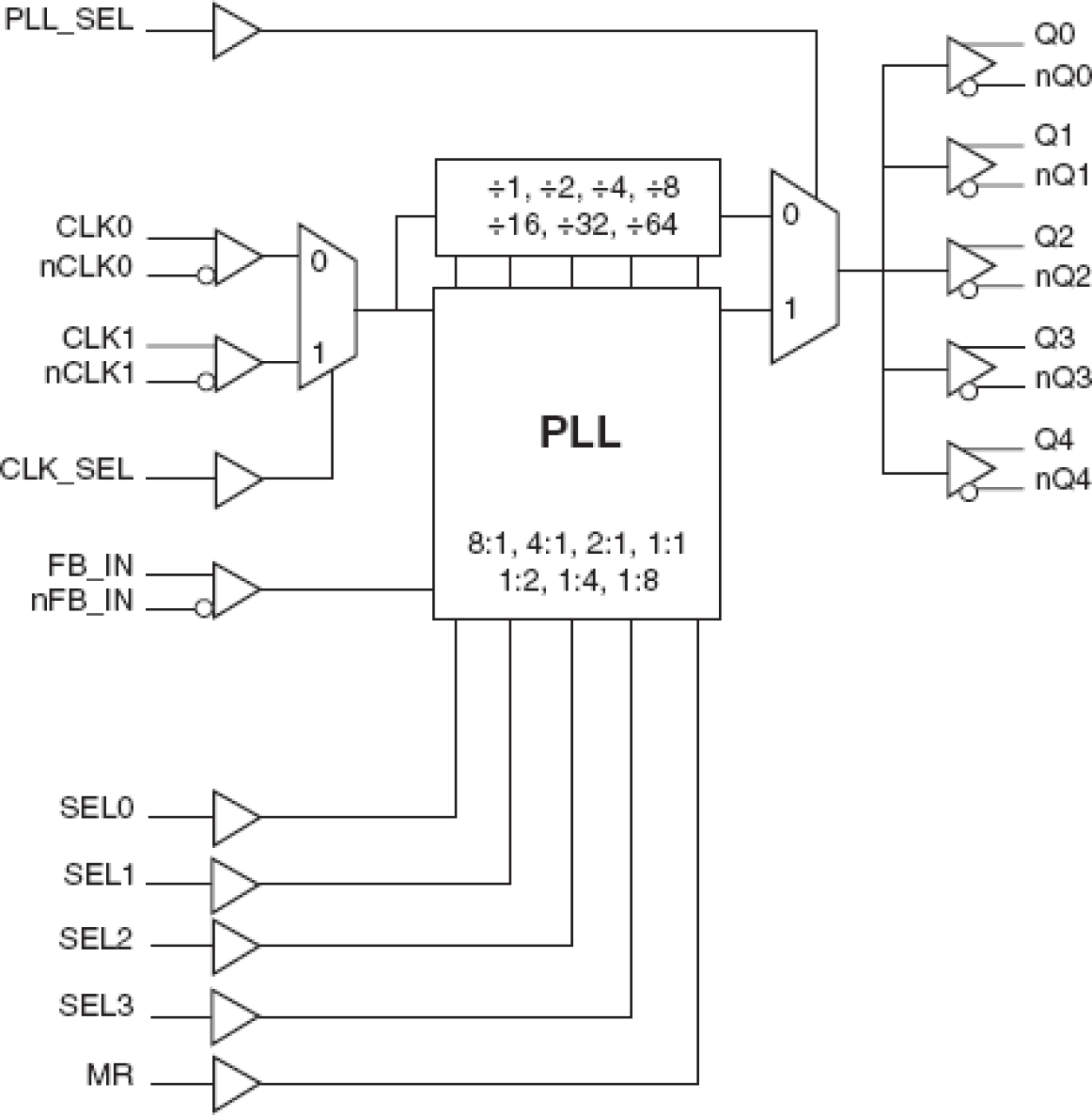

The 8725B-01 is a highly versatile 1:5 Differential-to-HSTL clock generator and a member of the HiPerClockS™ family of High Performance Clock Solutions from IDT. The 8725B-01 has a fully integrated PLL and can be configured as zero delay buffer, multiplier or divider, and has an output frequency range of 31.25MHz to 700MHz. The reference divider, feedback divider and output divider are each programmable, thereby allowing for the following output-to-input frequency ratios: 8:1, 4:1, 2:1, 1:1, 1:2, 1:4, 1:8. The external feedback allows the device to achieve "zero delay" between the input clock and the output clocks. The PLL_SEL pin can be used to bypass the PLL for system test and debug purposes. In bypass mode, the reference clock is routed around the PLL and into the internal output dividers.