特性

- Fully integrated PLL

- 8 LVCMOS outputs, 7Ω typical output impedance

- Selectable LVCMOS CLK0 or CLK1 inputs for redundant clock applications

- Input/Output frequency range: 18.33MHz to 240MHz at VCC = 3.3V ± 5%

- VCO range: 220MHz to 480MHz

- External feedback for "zero delay" clock regeneration

- Cycle-to-cycle jitter: 75ps (maximum), (all outputs are the same frequency)

- Output skew: 100ps (maximum)

- Bank skew: 55ps (maximum)

- Full 3.3V or 2.5V supply voltage

- -40°C to 85°C ambient operating temperature

- Lead-Free package fully RoHS compliant

描述

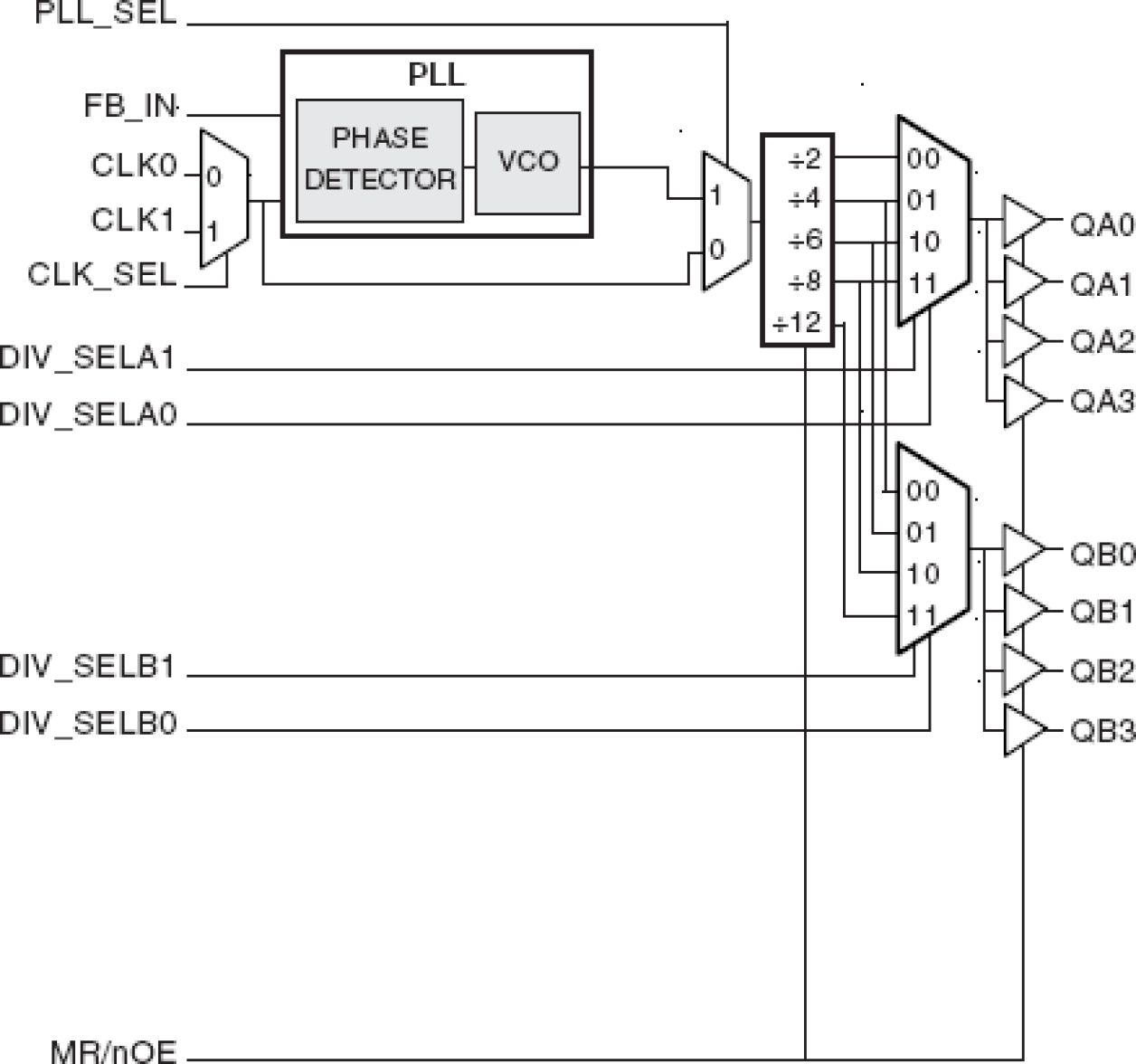

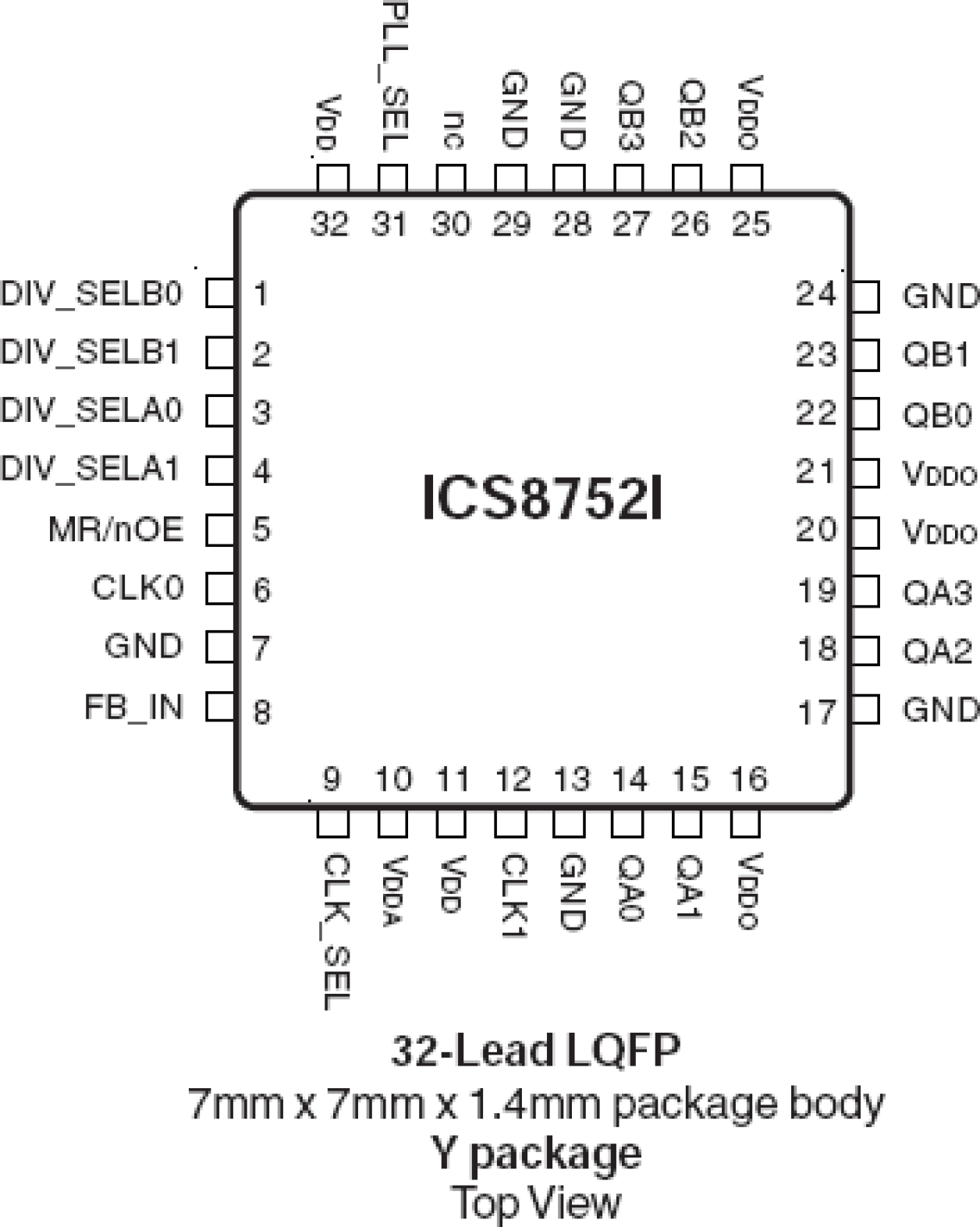

The 8752I is a low voltage, low skew LVCMOS clock generator. With output up to 240MHz, the 8752I is targeted for high performance clock applications. Along with a fully integrated PLL, the 8752I contains frequency configurable outputs and an external feedback input for regenerating clocks with "zero delay".

Dual clock inputs, CLK0 and CLK1, support redundant clock applications. The CLK_SEL input determines which reference clock is used. The output divider values of Bank A and B are controlled by the DIV_SELA0:1, and DIV_SELB0:1, respectively.

For test and system debug purposes, the PLL_SEL input allows the PLL to be bypassed. When HIGH, the MR/nOE input resets the internal dividers and forces the outputs to the high impedance state.

The low impedance LVCMOS outputs of the 8752I are designed to drive terminated transmission lines. The effective fanout of each output can be doubled by utilizing the ability of each output to drive two series terminated transmission lines.

当前筛选条件