封装信息

| CAD 模型: | View CAD Model |

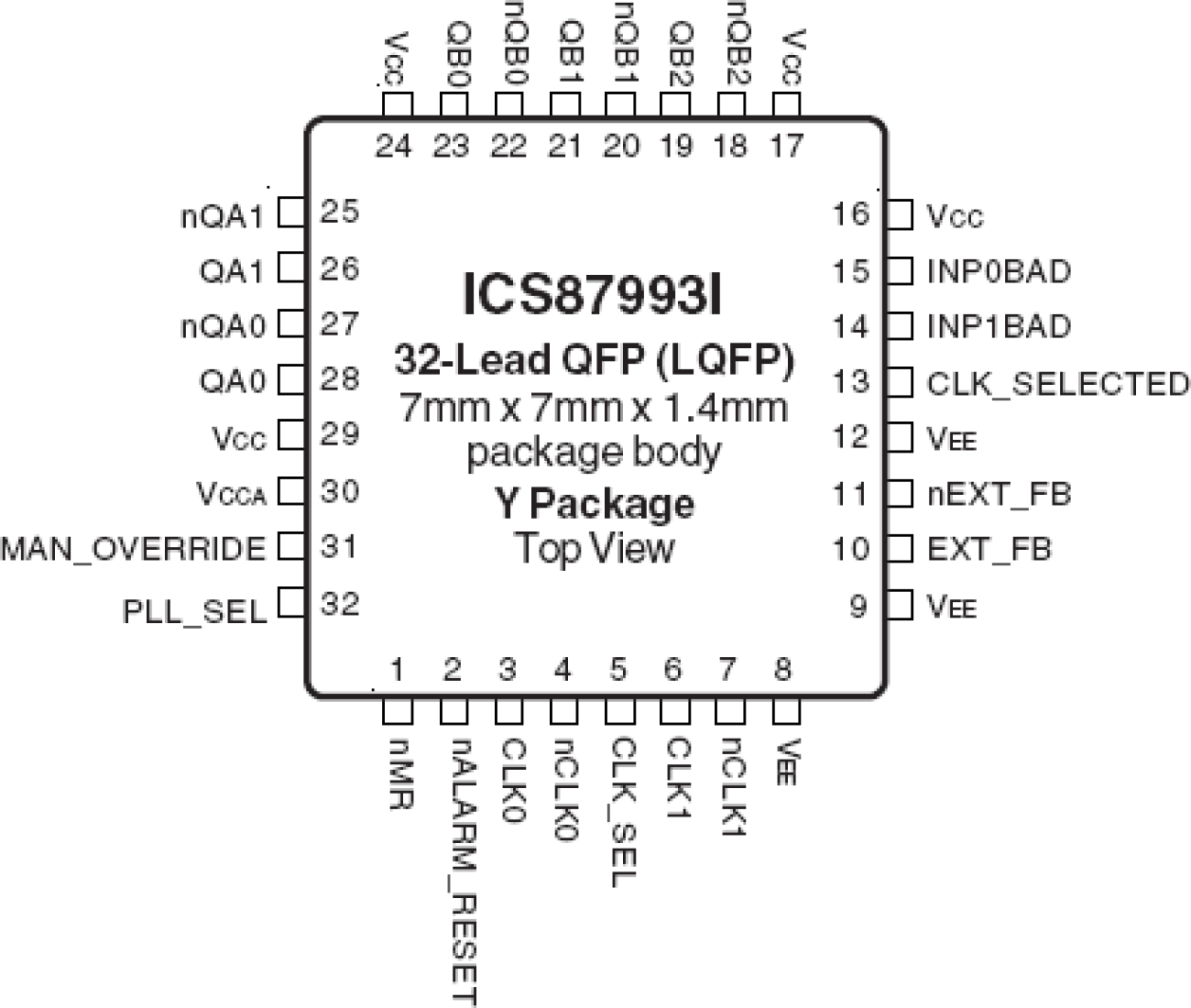

| Pkg. Type: | TQFP |

| Pkg. Code: | PRG32 |

| Lead Count (#): | 32 |

| Pkg. Dimensions (mm): | 7.0 x 7.0 x 1.4 |

| Pitch (mm): | 0.8 |

环境和出口类别

| Moisture Sensitivity Level (MSL) | 3 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

产品属性

| Lead Count (#) | 32 |

| Carrier Type | Reel |

| Moisture Sensitivity Level (MSL) | 3 |

| Qty. per Reel (#) | 2000 |

| Qty. per Carrier (#) | 0 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range (°C) | -40 to 85°C |

| Advanced Features | Feedback Input |

| C-C Jitter Max P-P (ps) | 20 |

| Core Voltage (V) | 3.3 |

| Feedback Input | Yes |

| Input Type | HCSL, HSTL, LVDS, LVPECL, SSTL |

| Inputs (#) | 2 |

| Length (mm) | 7 |

| MOQ | 2000 |

| Output Banks (#) | 2 |

| Output Freq Range (MHz) | 50 - 250 |

| Output Skew (ps) | 70 |

| Output Type | LVPECL |

| Output Voltage (V) | 3.3 |

| Outputs (#) | 5 |

| Package Area (mm²) | 49 |

| Pitch (mm) | 0.8 |

| Pkg. Dimensions (mm) | 7.0 x 7.0 x 1.4 |

| Pkg. Type | TQFP |

| Product Category | Zero Delay Buffers |

| Prog. Clock | No |

| Reel Size (in) | 13 |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Tape & Reel | Yes |

| Thickness (mm) | 1.4 |

| Width (mm) | 7 |

有关 87993I 的资源

描述

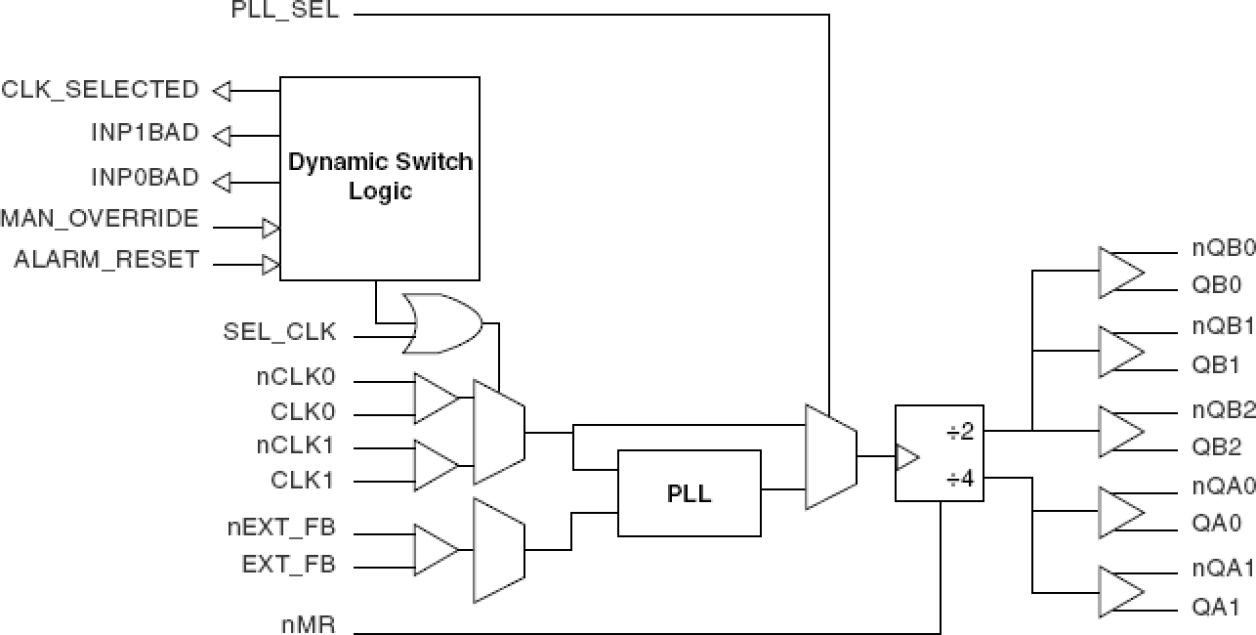

The 87993I is a PLL clock driver designed specifically for redundant clock tree designs. The device receives two differential LVPECL clock signals from which it generates 5 new differential LVPECL clock outputs. Two of the output pairs regenerate the input signal frequency and phase while the other three pairs generate 2x, phase aligned clock outputs. External PLL feedback is used to also provide zero delay buffer performance. The 87993I Dynamic Clock Switch (DCS) circuit continuously monitors both input CLK signals. Upon detection of a failure (CLK stuck HIGH or LOW for at least 1 period), the INP_BAD for that CLK will be latched (H). If that CLK is the primary clock, the DCS will switch to the good secondary clock and phase/frequency alignment will occur with minimal output phase disturbance. The typical phase bump caused by a failed clock is eliminated.