封装信息

| CAD 模型: | View CAD Model |

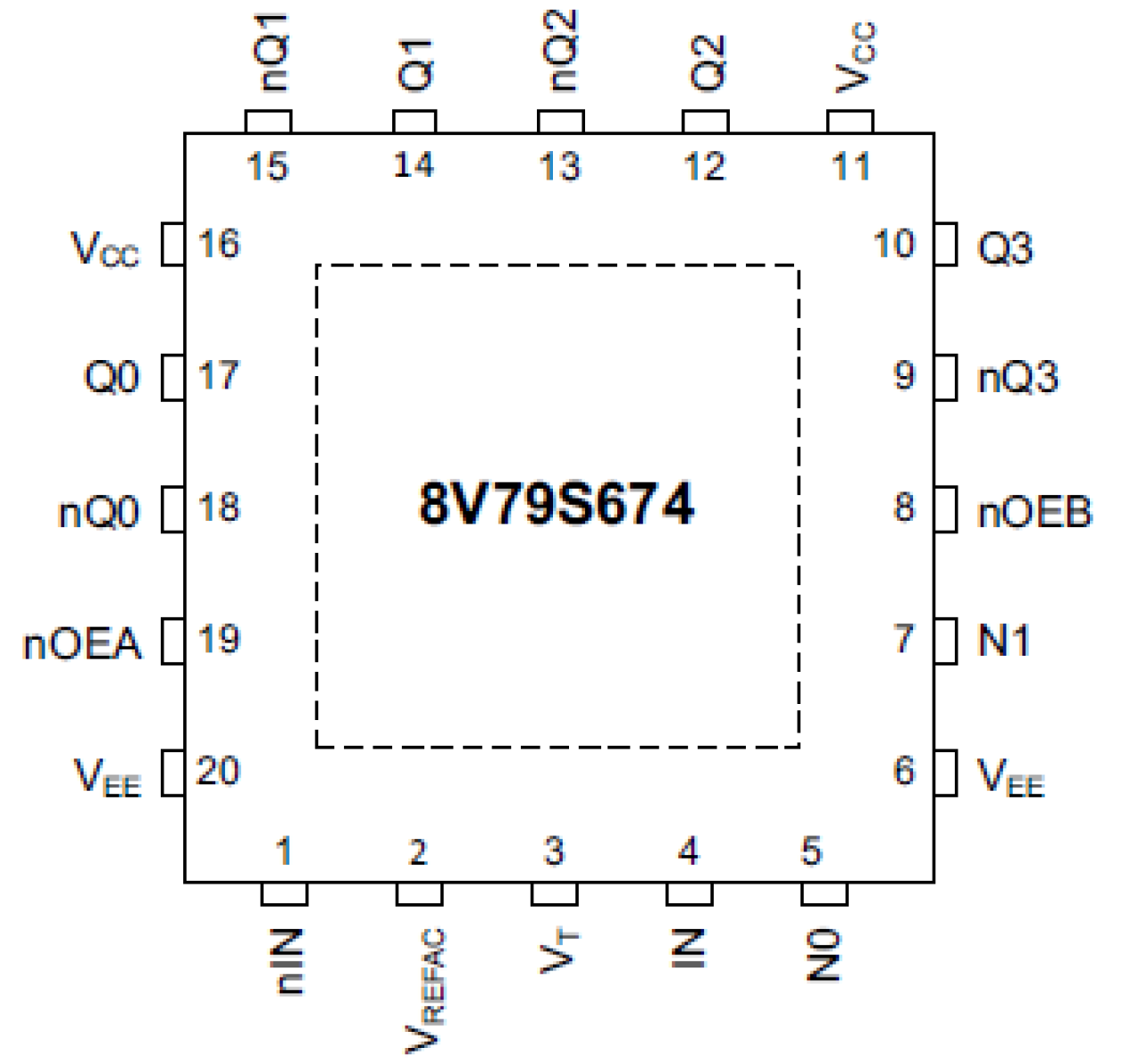

| Pkg. Type: | VFQFPN |

| Pkg. Code: | NLG20 |

| Lead Count (#): | 20 |

| Pkg. Dimensions (mm): | 4.0 x 4.0 x 1.0 |

| Pitch (mm): | 0.5 |

环境和出口类别

| Moisture Sensitivity Level (MSL) | 1 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

产品属性

| Lead Count (#) | 20 |

| Carrier Type | Reel |

| Moisture Sensitivity Level (MSL) | 1 |

| Qty. per Reel (#) | 2500 |

| Qty. per Carrier (#) | 0 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range (°C) | -40 to 85°C |

| Additive Phase Jitter Typ RMS (fs) | 42 |

| Additive Phase Jitter Typ RMS (ps) | 0.042 |

| Adjustable Phase | No |

| Channels (#) | 1 |

| Core Voltage (V) | 2.5V, 3.3V |

| Divider Value | 1, 2, 4, 8 |

| Function | Buffer, Divider |

| Input Freq (MHz) | 2500 |

| Input Type | LVDS, LVPECL |

| Inputs (#) | 1 |

| Length (mm) | 4 |

| MOQ | 2500 |

| Noise Floor (dBc/Hz) | -163 |

| Output Banks (#) | 1 |

| Output Freq Range (MHz) | 2500, 1250, 625, 312.5 |

| Output Skew (ps) | 22 |

| Output Type | LVPECL |

| Output Voltage (V) | 2.5V, 3.3V |

| Outputs (#) | 4 |

| Package Area (mm²) | 16 |

| Pitch (mm) | 0.5 |

| Pkg. Dimensions (mm) | 4.0 x 4.0 x 1.0 |

| Pkg. Type | VFQFPN |

| Product Category | Clock Buffers & Drivers, Clock Dividers, RF Buffers |

| Reel Size (in) | 13 |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Supply Voltage (V) | 2.5 - 2.5, 3.3 - 3.3 |

| Tape & Reel | Yes |

| Thickness (mm) | 1 |

| Width (mm) | 4 |

有关 8V79S674 的资源

描述

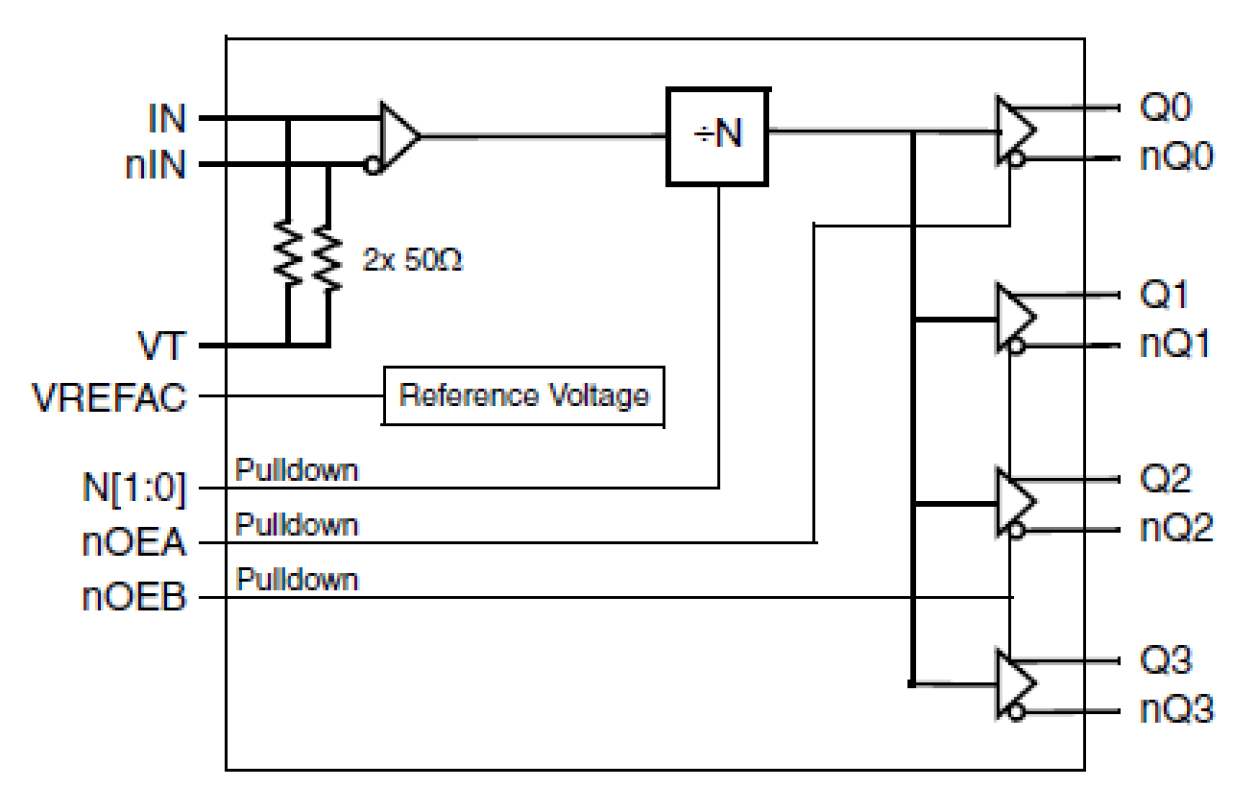

The 8V79S674 is a clock divider and fanout buffer designed for clock signal division in wireless base station radio equipment boards. The device is optimized to deliver excellent additive phase jitter performance. The 8V79S674 uses SiGe technology for an optimum of high clock frequency and low phase noise performance, combined with high power supply noise rejection. It offers the frequency division by ÷1, ÷2, ÷4 and ÷8. Four low-skew LVPECL outputs are available and support clock output frequencies up to 2.5GHz (÷1 frequency division). Outputs can be disabled to save power consumption if not used. The device is packaged in a lead-free (RoHS 6) 20-lead VFQFN package. The extended temperature range supports wireless infrastructure, telecommunication, and networking end equipment requirements.