封装信息

| CAD 模型: | View CAD Model |

| Pkg. Type: | VFQFPN |

| Pkg. Code: | NLG72 |

| Lead Count (#): | 72 |

| Pkg. Dimensions (mm): | 10.0 x 10.0 x 1.0 |

| Pitch (mm): | 0.5 |

环境和出口类别

| Moisture Sensitivity Level (MSL) | 3 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

产品属性

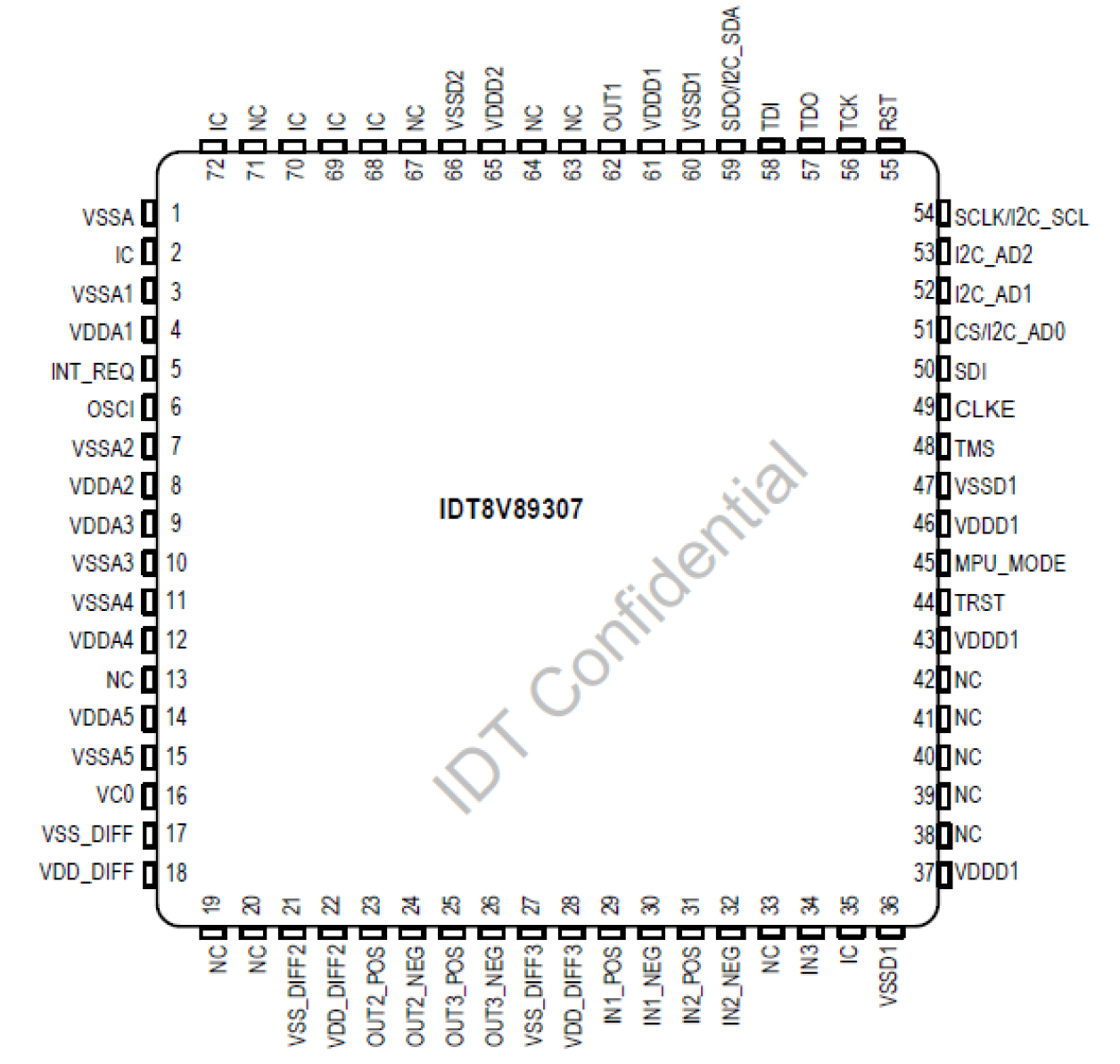

| Lead Count (#) | 72 |

| Carrier Type | Reel |

| Moisture Sensitivity Level (MSL) | 3 |

| Qty. per Reel (#) | 2500 |

| Qty. per Carrier (#) | 0 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range (°C) | 0 to 70°C |

| Country of Assembly | CHINA |

| Country of Wafer Fabrication | TAIWAN |

| Advanced Features | Microprocessor interface modes, JTAG boundary scan |

| Core Voltage (V) | 3.3 |

| Fractional Output Dividers (#) | 3 |

| Input Freq (MHz) | 1 - 625 |

| Input Type | LVPECL, LVCMOS, LVDS |

| Inputs (#) | 3 |

| Length (mm) | 10 |

| Loop Bandwidth Range (Hz) | 15 - 560 |

| MOQ | 2500 |

| Output Banks (#) | 3 |

| Output Freq Range (MHz) | 1 - 644.531 |

| Output Type | LVPECL, LVCMOS, LVDS |

| Output Voltage (V) | 3.3 |

| Outputs (#) | 3 |

| Package Area (mm²) | 100 |

| Phase Jitter Typ RMS (ps) | 1 |

| Pitch (mm) | 0.5 |

| Pkg. Dimensions (mm) | 10.0 x 10.0 x 1.0 |

| Pkg. Type | VFQFPN |

| Product Category | FemtoClock NG, Jitter Attenuators |

| Reel Size (in) | 13 |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Tape & Reel | Yes |

| Thickness (mm) | 1 |

| Width (mm) | 10 |

| Xtal Freq (KHz) | 12800 - 12800 |

有关 8V89307 的资源

描述

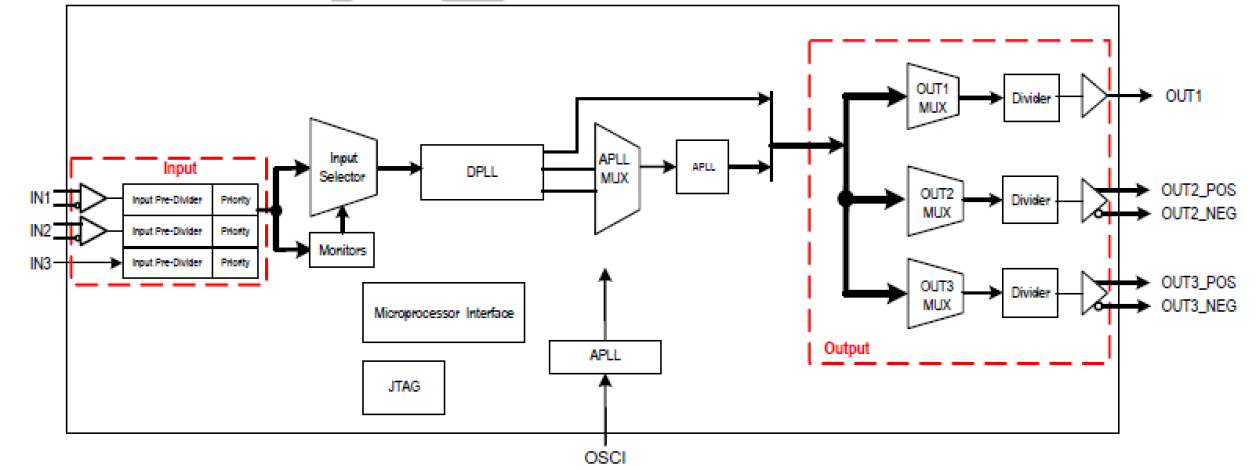

The 8V89307 is an integrated solution for the Synchronous Equipment Timing Source supporting EEC-Option1 and EEC-Option2 clocks in Synchronous Ethernet equipment. The device has a high-quality DPLL to provide system clocks for node timing synchronization within a Synchronous Ethernet network. It also integrates an APLL for better jitter performance.

An input clock is automatically or manually selected. It supports three primary operating modes: Free-Run, Locked, and Holdover. In Free-Run mode, the DPLL refers to the master clock. In Locked mode, the DPLL locks to the selected input clock. In Holdover mode, the DPLL resorts to the frequency data acquired in Locked mode. Whatever the operating mode is, the DPLL gives a stable performance without being affected by operating conditions or silicon process variations.

The device provides programmable DPLL bandwidths: 15MHz to 560Hz and damping factors: 1.2 to 20 in 5 steps. Different settings cover all clock synchronization requirements.

A stable oscillator is required for the master clock in different applications. The master clock is used as a reference clock for all the internal circuits in the device. It can be calibrated within ±741ppm.

All the read/write registers are accessed through a microprocessor interface. The device supports Serial and I2C interfaces.