封装信息

| CAD 模型: | View CAD Model |

| Pkg. Type: | TSSOP |

| Pkg. Code: | PAG48 |

| Lead Count (#): | 48 |

| Pkg. Dimensions (mm): | 12.5 x 6.1 x 1.0 |

| Pitch (mm): | 0.5 |

环境和出口类别

| Moisture Sensitivity Level (MSL) | 1 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

产品属性

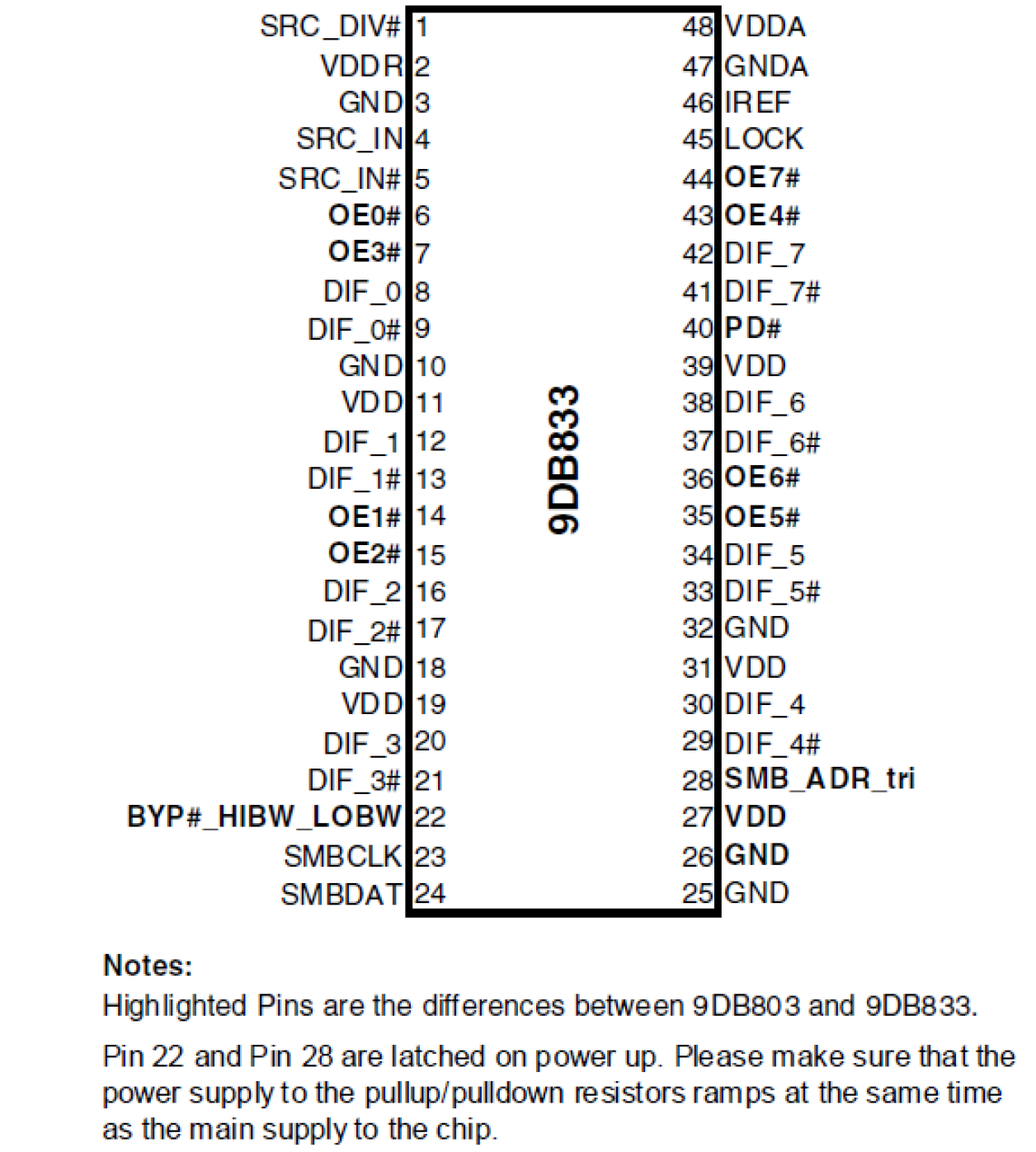

| Lead Count (#) | 48 |

| Carrier Type | Reel |

| Moisture Sensitivity Level (MSL) | 1 |

| Qty. per Reel (#) | 2000 |

| Qty. per Carrier (#) | 0 |

| Package Area (mm²) | 76.3 |

| Pitch (mm) | 0.5 |

| Pkg. Dimensions (mm) | 12.5 x 6.1 x 1.0 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range (°C) | -40 to 85°C |

| Country of Assembly | TAIWAN |

| Country of Wafer Fabrication | SINGAPORE |

| Accepts Spread Spec Input | Yes |

| Advanced Features | HW PLL mode control |

| App Jitter Compliance | PCIe Gen1, PCIe Gen2, PCIe Gen3 |

| Architecture | Common |

| C-C Jitter Max P-P (ps) | 50 |

| C-C Jitter Typ P-P (ps) | 25 |

| Chipset Name | Blackford, Clarksboro, Greencreek, Lindenhurst, Twincastle, San Clemente, Seaburg, Tylersburg |

| Clock Spec. | DB800 Gen3 |

| Core Voltage (V) | 3.3 |

| Diff. Input Signaling | HCSL |

| Diff. Inputs | 1 |

| Diff. Output Signaling | HCSL |

| Diff. Outputs | 8 |

| Diff. Termination Resistors | 32 |

| Feedback Input | No |

| Function | Zero Delay Buffer |

| Input Freq (MHz) | 50 - 100 |

| Input Type | HCSL |

| Inputs (#) | 1 |

| Length (mm) | 12.5 |

| MOQ | 2000 |

| Multiplication Value | 1 |

| Output Banks (#) | 1 |

| Output Freq Range (MHz) | 5 - 166.66 |

| Output Skew (ps) | 50 |

| Output Type | HCSL |

| Output Voltage (V) | 0.8 |

| Outputs (#) | 8 |

| PLL | Yes |

| Pkg. Type | TSSOP |

| Platform Name | Bensley, Caneland, Glidewell, Lindenhurst, Truland, Stoakley, Thurley, Cranberry Lake |

| Power Consumption Typ (mW) | 528 |

| Price (USD) | $3.19168 |

| Product Category | PCI Express Clocks |

| Prog. Clock | No |

| Reel Size (in) | 13 |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Supply Voltage (V) | 3.3 - 3.3 |

| Tape & Reel | Yes |

| Thickness (mm) | 1 |

| Width (mm) | 6.1 |

有关 9DB833 的资源

描述

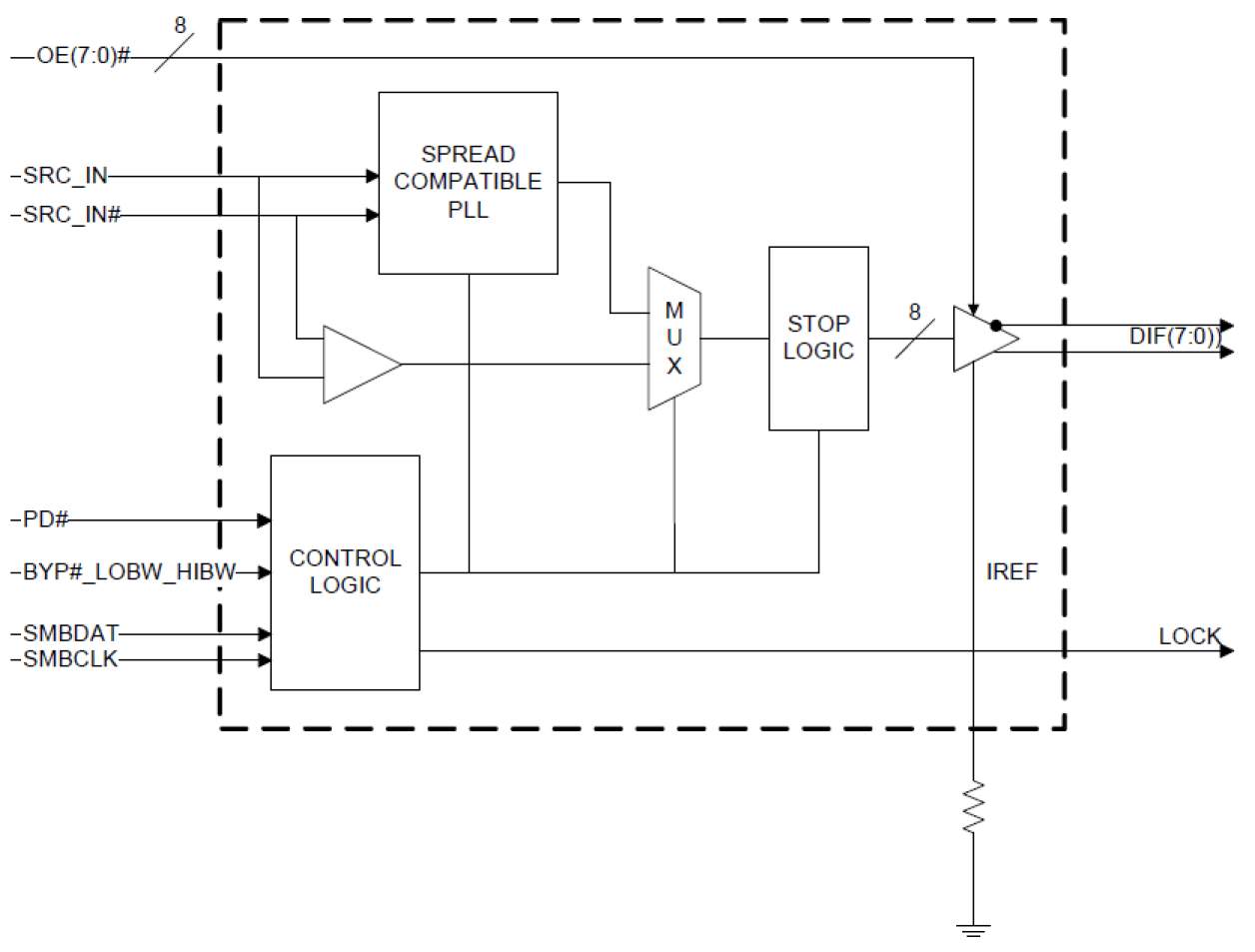

The 9DB833 zero delay buffer (ZDB) supports PCIe Gen3 requirements while being backward compatible with PCIe Gen2 and Gen1. The 9DB833 is driven by a differential SRC output pair from a 932S421 or 932SQ420 or equivalent main clock generator.