特性

- PCIe Gen 1–7 CC compliant

- PCIe Gen 1–7 SRIS compliant

- Supports PCIe SRnS clocking

- Direct connection to 100Ω (xx42) or 85Ω (xx52) transmission lines; saves 16 resistors compared to standard PCIe devices

- Spread spectrum tolerant; allows reduction of EMI

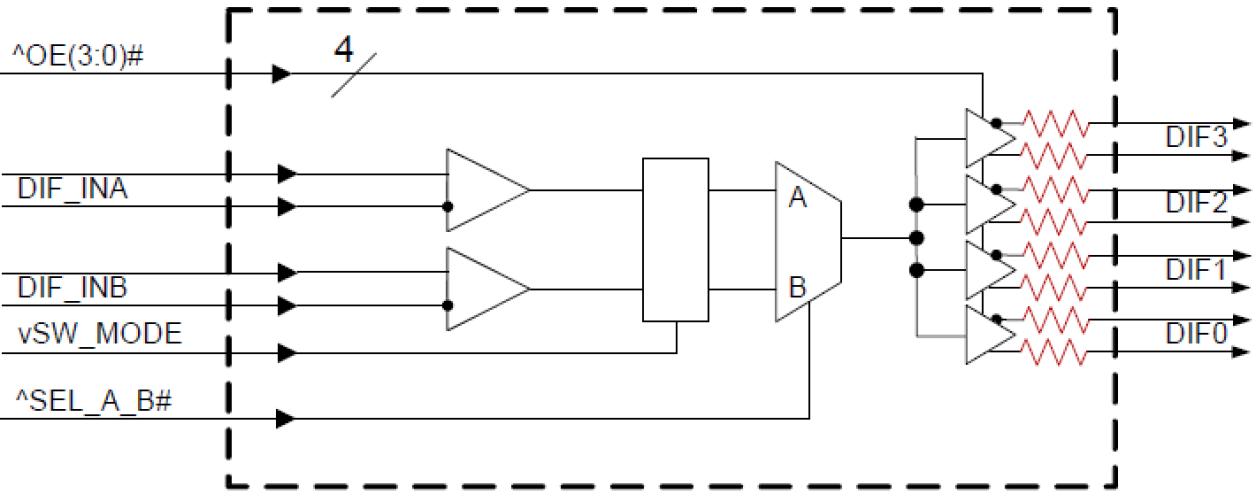

- Selectable asynchronous or glitch-free switching; allows the mux to be selected at power up even if both inputs are not running, then transition to glitch-free switching mode

- Easy AC coupling to other logic families, see application note AN-891.

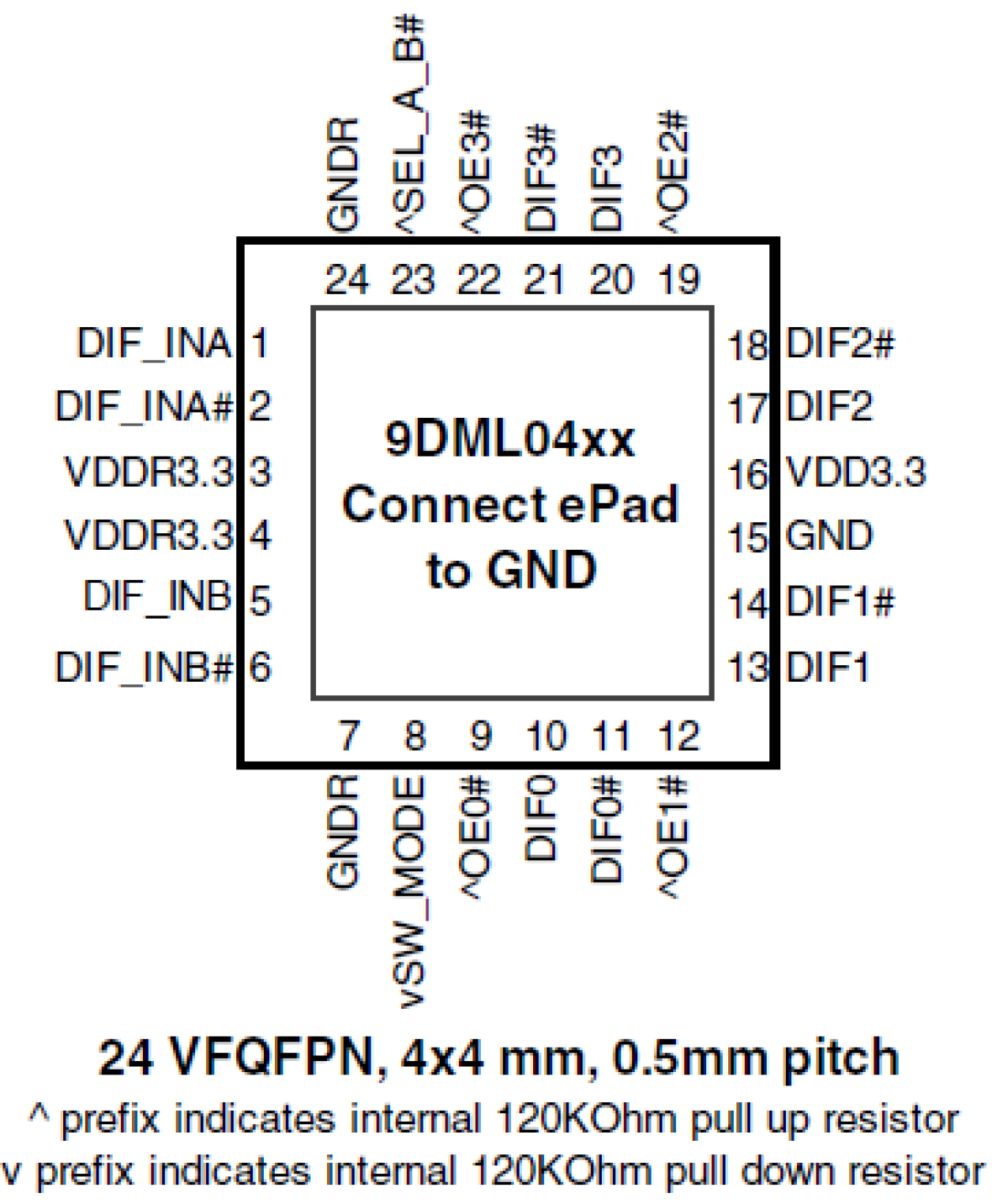

- Space saving 4mm × 4mm 24-VFQFPN; minimal board space

描述

The 9DML04 devices are 3.3V members of Renesas' full-featured PCIe family. The 9DML04 supports PCIe Gen 1–7 Common Clocked (CC), Separate Reference no Spread (SRnS), and Separate Reference Independent Spread (SRIS) architectures. The part provides a choice of asynchronous and glitch-free switching modes and offers a choice of integrated output terminations providing direct connection to 85Ω or 100Ω transmission lines. The 9DML04P1 can be factory programmed with a user-defined power-up default SMBus configuration.

For information regarding evaluation boards and material, please contact your local sales representative.

产品参数

| 属性 | 值 |

|---|---|

| Diff. Outputs | 4 |

| Diff. Output Signaling | LP-HCSL |

| Output Freq Range (MHz) | 1 - 200 |

| Diff. Inputs | 2 |

| Diff. Input Signaling | HCSL |

| Accepts Spread Spec Input | Yes |

| Power Consumption Typ (mW) | 76 |

| Supply Voltage (V) | 3.3 - 3.3 |

| Output Type | LP-HCSL |

| Diff. Termination Resistors | 0 |

| Package Area (mm²) | 16 |

| Battery Backup | No |

| Battery Seal | No |

| CPU Supervisory Function POR | No |

| Crystal Frequency Trimming | No |

| Frequency Out Pin | No |

| Inputs (#) | 2 |

| Input Freq (MHz) | 1 - 200 |

| Additive Phase Jitter Typ RMS (fs) | 350 |

| Function | Multiplexer |

| Input Type | HCSL |

| Output Banks (#) | 1 |

| Core Voltage (V) | 3.3 |

| Output Voltage (V) | 0.8 |

| Product Category | Clock Multiplexers, PCI Express Clocks |

封装选项

| Pkg. Type | Pkg. Dimensions (mm) | Lead Count (#) | Pitch (mm) |

|---|---|---|---|

| VFQFPN | 4.0 x 4.0 x 0.9 | 24 | 0.5 |

应用

- Servers

- ATE

- Storage

- Master/Slave applications

当前筛选条件