特性

- 19 LP-HCSL differential output pairs with integrated terminations (Zo = 85Ω)

- LP-HCSL outputs; up to 90% IO power reduction, better signal integrity over long traces

- Direct connect to 85Ω transmission lines; eliminates 76 termination resistors, saves 130mm² area

- Pin compatible with the 9ZXL1930; easy upgrade to reduced board space

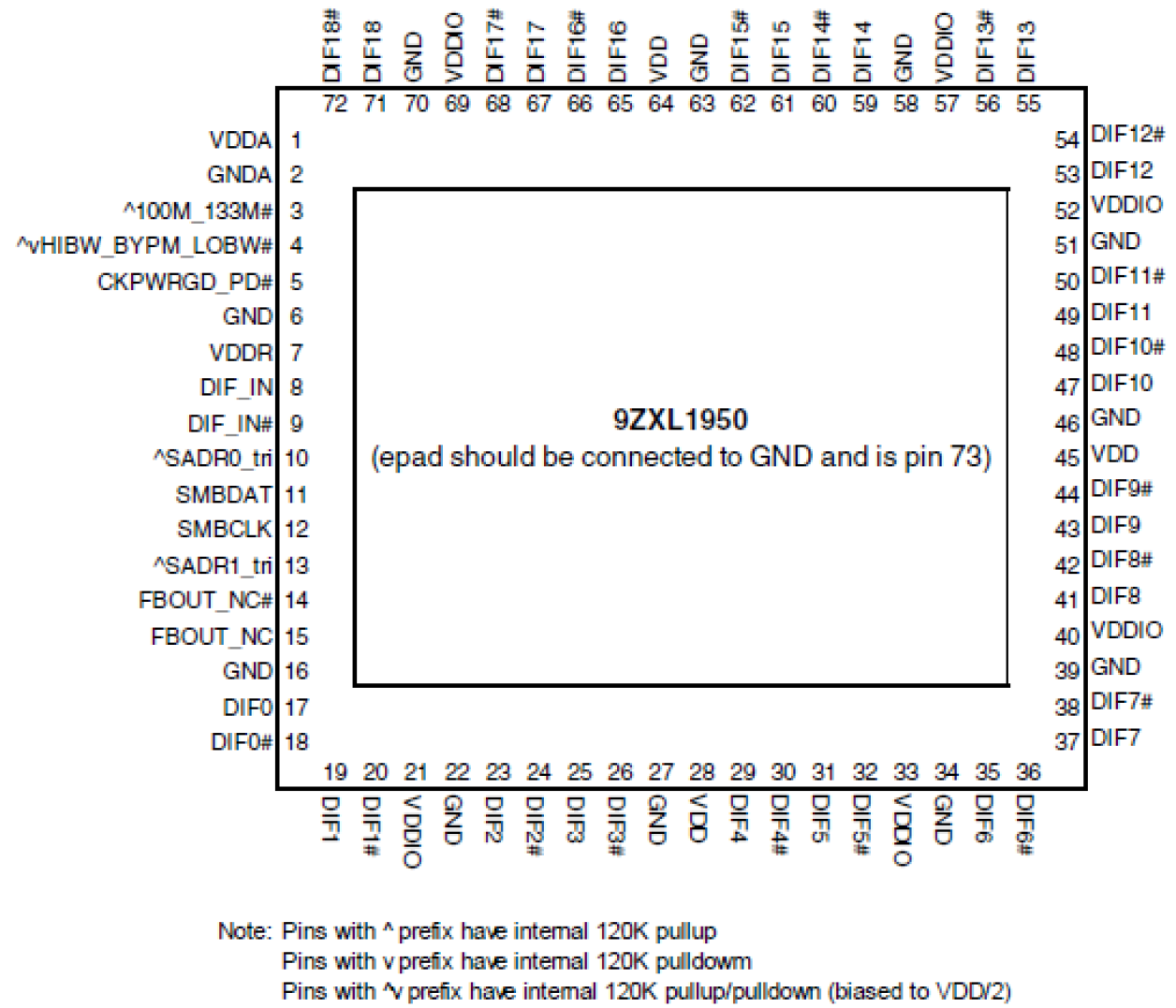

- 72-VFQFPN package; smallest 19 output Z-buffer

- Fixed feedback path; ~0ps input-to-output delay

- 9 selectable SMBus addresses; multiple devices can share the same SMBus segment

- Separate VDDIO for outputs; allows maximum power savings

- PLL or bypass mode; PLL can de-jitter incoming clock

- 100MHz and 133.33MHz PLL mode; legacy QPI support

- Selectable PLL BW; minimizes jitter peaking in downstream PLLs

- Spread spectrum compatible; tracks spreading input clock for EMI reduction

- SMBus interface; unused outputs can be disabled

描述

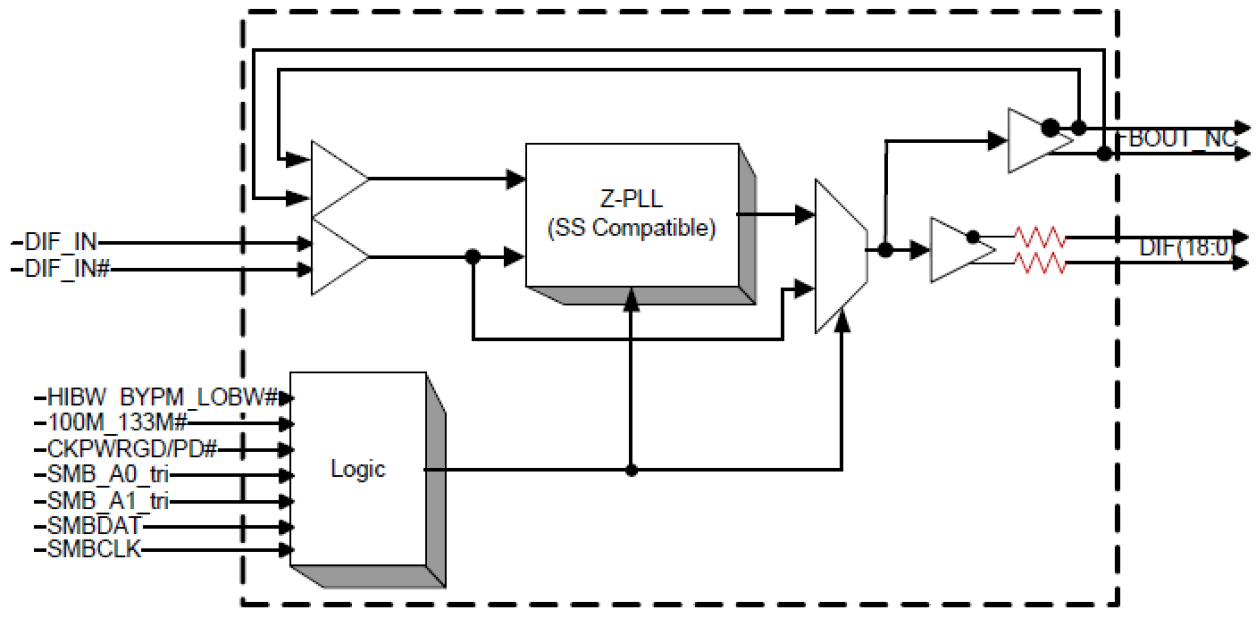

The 9ZXL1950 is a DB1900Z derivative buffer utilizing Low-Power HCSL (LP-HCSL) outputs to increase edge rates on long traces, reduce board space, and reduce power consumption by more than 50% from the original 9ZX21901. It is pin-compatible with the 9ZXL1930 and fully integrates the output terminations. The 9ZXL1950 is suitable for PCI Express Gen 1/2/3 or QPI/UPI applications and uses fixed external feedback to maintain low drift for demanding QPI/UPI applications.

产品参数

| 属性 | 值 |

|---|---|

| Diff. Outputs | 19 |

| Diff. Output Signaling | LP-HCSL |

| Output Freq Range (MHz) | 33 - 150 |

| Diff. Inputs | 1 |

| Diff. Input Signaling | HCSL |

| Accepts Spread Spec Input | Yes |

| Power Consumption Typ (mW) | 614 |

| Supply Voltage (V) | 1.05 - 3.3 |

| Output Type | LP-HCSL |

| Diff. Termination Resistors | 0 |

| Package Area (mm²) | 100 |

| Battery Backup | No |

| Battery Seal | No |

| CPU Supervisory Function POR | No |

| Crystal Frequency Trimming | No |

| Frequency Out Pin | No |

| Inputs (#) | 1 |

| Input Freq (MHz) | 33 - 150 |

| Function | Buffer |

| Input Type | HCSL |

| Output Banks (#) | 1 |

| Core Voltage (V) | 3.3 |

| Output Voltage (V) | 0.7 |

| Product Category | Processor Clock Buffers, Zero Delay Buffers |

封装选项

| Pkg. Type | Pkg. Dimensions (mm) | Lead Count (#) | Pitch (mm) |

|---|---|---|---|

| VFQFPN | 10.0 x 10.0 x 1.0 | 72 | 0.5 |

当前筛选条件