封装信息

| CAD 模型: | View CAD Model |

| Pkg. Type: | QFN |

| Pkg. Code: | LBE |

| Lead Count (#): | 20 |

| Pkg. Dimensions (mm): | 4.0 x 4.0 x 0.90 |

| Pitch (mm): | 0.5 |

环境和出口类别

| Moisture Sensitivity Level (MSL) | 3 |

| Pb (Lead) Free | Yes |

| RoHS (ISL6271ACRZ) | 下载 |

| ECCN (US) | |

| HTS (US) |

产品属性

| Lead Count (#) | 20 |

| Carrier Type | Tube |

| Moisture Sensitivity Level (MSL) | 3 |

| Pb (Lead) Free | Yes |

| Pb Free Category | Pb-Free 100% Matte Tin Plate w/Anneal-e3 |

| Temp. Range (°C) | 0 to +70°C |

| Bias Voltage Range (V) | 3.7 - 3.7 |

| DDR Capable | No |

| Input Voltage (Max) (V) | 5.5 |

| Input Voltage (Max) [Rail 1] (V) | 5.5 - 5.5 |

| Input Voltage (Min) (V) | 2.76 |

| Input Voltage (Min) [Rail 1] (V) | 2.76 |

| Length (mm) | 4 |

| Linear Output | Yes |

| MOQ | 750 |

| Output Current (Max) [Rail 1] (A) | 0.8 |

| Output Current 1 (Max) (A) | 0.8 |

| Output Current 2 (Max) (A) | 0.05 |

| Output Voltage (Max) [Rail 1] (V) | 1.6 |

| Output Voltage (Min) (V) | 0.85 |

| Output Voltage (Min) [Rail 1] (V) | 0.85 |

| Output Voltage 1 (Max) (V) | 1.6 |

| Output Voltage 2 (Max) | 1.1 |

| Output Voltage 3 (Max) | 1.3 |

| Outputs (#) | 3 |

| Parametric Category | Buck Controllers (External FETs) |

| Pitch (mm) | 0.5 |

| Pkg. Dimensions (mm) | 4.0 x 4.0 x 0.90 |

| Pkg. Type | QFN |

| Qualification Level | Standard |

| Switching Frequency Range (Typical) (kHz) | 1200 - 1200 |

| Thickness (mm) | 0.9 |

| Topology [Rail 1] | Buck |

| Width (mm) | 4 |

有关 ISL6271A 的资源

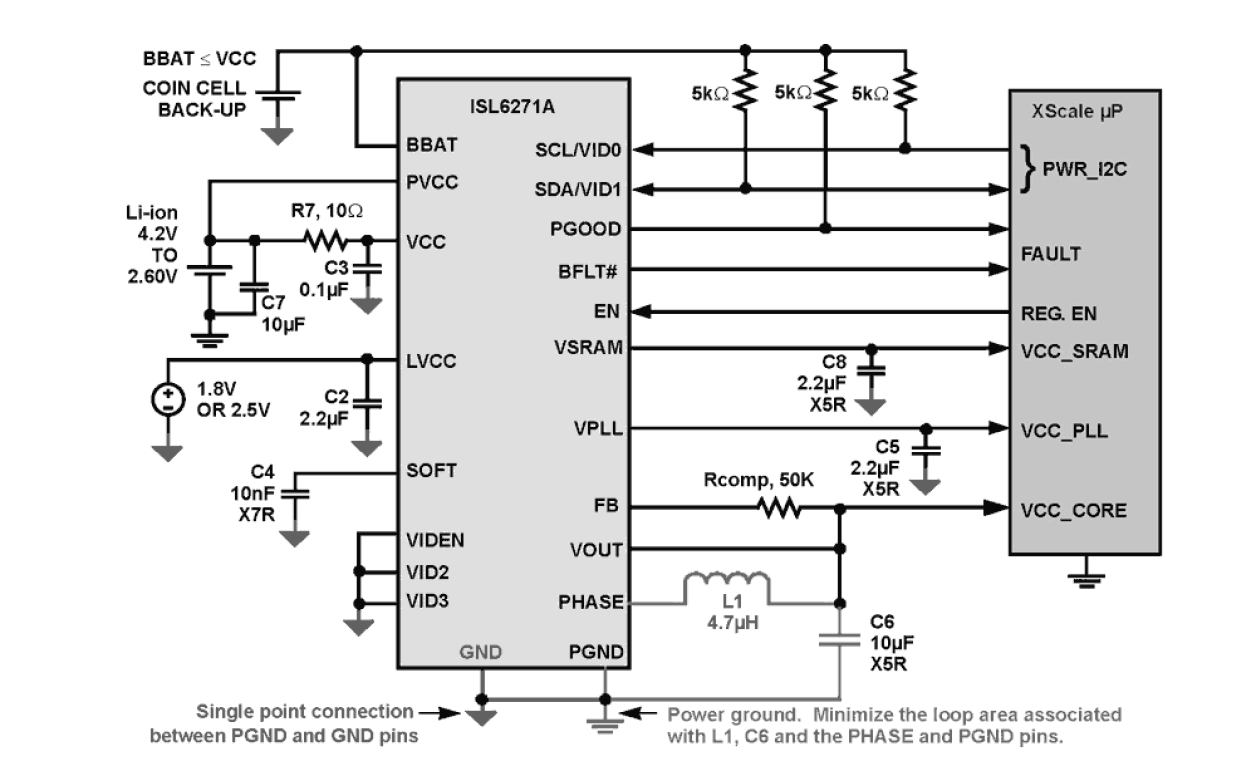

描述

The ISL6271A is a versatile power management IC (PMIC) designed for the Xscale type of processors. The device integrates three regulators, two fault indicators and an I2C bus for communication with a host microprocessor. Two of the three regulators function as low power, low drop out regulators, designed to power SRAM and phase-lock loop circuitry internal to the Xscale processor. The third regulator uses a proprietary switch-mode topology to power the processor core and facilitate Dynamic Voltage Management (DVM), as defined by Intel. Since power dissipation inside a microprocessor is proportional to the square of the core voltage, Intel XScale processors implement DVM as a means to more efficiently utilize battery capacity. To support this power saving architecture, the ISL6271A integrates an I2C bus for communication with the host processor. The processor, acting as the bus master, transmits a voltage level and voltage slew rate to the ISL6271A appropriate to the processing requirements; higher core voltages support higher operating frequencies and code execution. The bus is fully compliant with the Phillips® I2C protocol and supports both standard and fast data transmission modes. Alternatively, the output of the core regulator can be programmed in 50mV increments from 0.85V to 1.6V using the input Voltage ID (VID) pins. All three regulators share a common enable pin and are protected against overcurrent, over temperature and undervoltage conditions. When disabled via the enable pin, the ISL6271A enters a low power state that can be used to conserve battery life while maintaining the last programmed VID code and slew rate. An integrated soft-start circuit transitions the ISL6271A output voltages to their default values at a rate determined by an external soft-start capacitor.