封装信息

| CAD 模型: | View CAD Model |

| Pkg. Type: | DFN |

| Pkg. Code: | LHU |

| Lead Count (#): | 10 |

| Pkg. Dimensions (mm): | 3.00 x 3.00 x 0.90 |

| Pitch (mm): | 0.5 |

环境和出口类别

| Moisture Sensitivity Level (MSL) | |

| Pb (Lead) Free | No |

| ECCN (US) | |

| HTS (US) |

产品属性

| Lead Count (#) | 10 |

| Carrier Type | Reel |

| Pb (Lead) Free | No |

| Temp. Range (°C) | -40 to +85°C |

| Drop Out Voltage (Typical) | 250 @ 300mA |

| Enable/Shutdown | Yes |

| External Bias | No |

| Fixed Output Voltage Option | Yes |

| Input Voltage (Max) (V) | 6.5 |

| Input Voltage (Min) (V) | 2.3 |

| Input Voltage Range (V) | 2.3 - 6.5 |

| Length (mm) | 3 |

| MOQ | 6000 |

| Noise (10Hz to 100kHz) (μVrms) | 30 |

| O/P Voltage Accuracy (±%) | 1.8 |

| Output Current 1 (Max) (A) | 0.15 |

| Output Current 2 (Max) (A) | 0.3 |

| Output Voltage (Max) (V) | 3.3 |

| Output Voltage (Min) (V) | 1.5 |

| Output Voltage Range (V) | 1.5 - 3.3 |

| PGOOD Output | No |

| PORs (#) | 1 |

| PSRR (db) | 70 |

| Parametric Category | Linear Regulators (LDO) |

| Pitch (mm) | 0.5 |

| Pkg. Dimensions (mm) | 3.0 x 3.0 x 0.90 |

| Pkg. Type | DFN |

| Qualification Level | Standard |

| Quiescent Current | 45 µA |

| Thickness (mm) | 0.9 |

| Width (mm) | 3 |

有关 ISL9012 的资源

描述

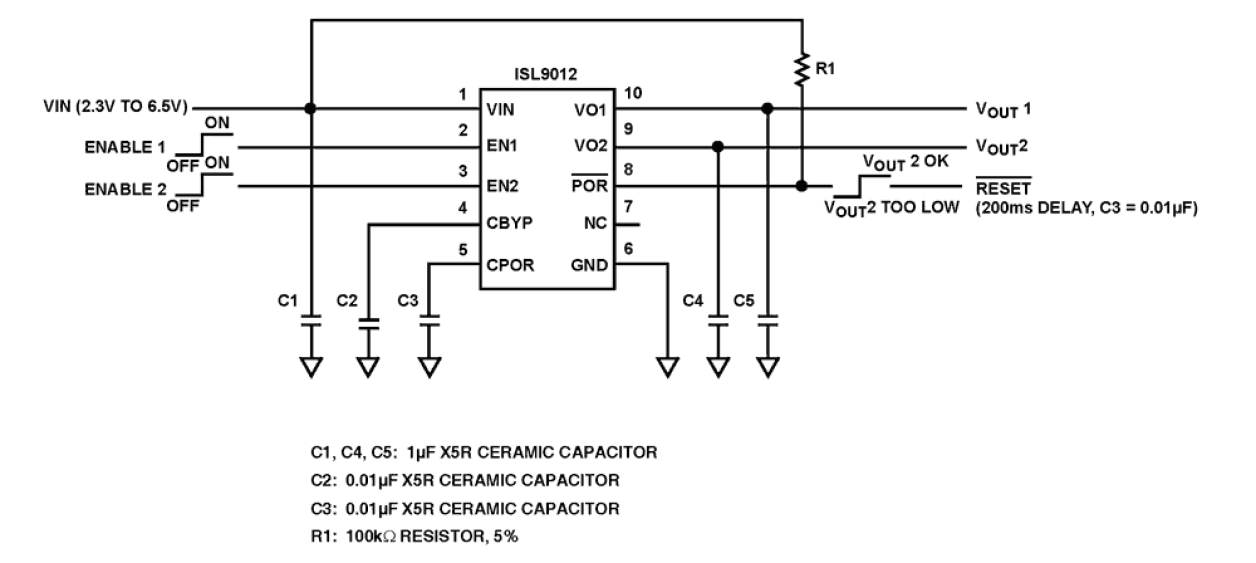

ISL9012 is a high performance dual LDO capable of sourcing 150mA current from Channel 1, and 300mA from Channel 2. The device has a low standby current and high-PSRR and is stable with output capacitance of 1µF to 10µF with ESR of up to 200mΩ. The device integrates a Power-On-Reset (POR) function for the VO2 output. The POR delay for VO2 can be externally programmed by connecting a timing capacitor to the CPOR pin. A reference bypass pin is also provided for connecting a noise-filtering capacitor for low noise and high PSRR applications. The quiescent current is typically only 45µA with both LDO's enabled and active. Separate enable pins control each individual LDO output. When both enable pins are low, the device is in shutdown, typically drawing less than 0. 1µA. Several combinations of voltage outputs are standard. Output voltage options for each LDO range from 1. 5V to 3. 3V. Other output voltage options are available on request.