封装信息

| CAD 模型: | View CAD Model |

| Pkg. Type: | TSSOP |

| Pkg. Code: | PAG56 |

| Lead Count (#): | 56 |

| Pkg. Dimensions (mm): | 14.0 x 6.1 x 1.0 |

| Pitch (mm): | 0.5 |

环境和出口类别

| Moisture Sensitivity Level (MSL) | 1 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

产品属性

| Lead Count (#) | 56 |

| Carrier Type | Reel |

| Moisture Sensitivity Level (MSL) | 1 |

| Qty. per Reel (#) | 2000 |

| Qty. per Carrier (#) | 0 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range (°C) | -40 to 85°C |

| Abs. Pull Range Min. (± PPM) | 115 |

| Core Voltage (V) | 3.3 |

| Feedback Input | No |

| Input Freq (MHz) | 0.001 - 170 |

| Input Type | LVCMOS |

| Inputs (#) | 3 |

| Length (mm) | 14 |

| MOQ | 2000 |

| Output Banks (#) | 3 |

| Output Freq Range (MHz) | 0.5 - 160 |

| Output Type | LVCMOS |

| Output Voltage (V) | 3.3 |

| Outputs (#) | 3 |

| Package Area (mm²) | 85.4 |

| Phase Jitter Typ RMS (ps) | 80 |

| Pitch (mm) | 0.5 |

| Pkg. Dimensions (mm) | 14.0 x 6.1 x 1.0 |

| Pkg. Type | TSSOP |

| Product Category | Jitter Attenuators |

| Prog. Clock | No |

| Reel Size (in) | 13 |

| Reference Output | Yes |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Spread Spectrum | No |

| Tape & Reel | Yes |

| Thickness (mm) | 1 |

| Width (mm) | 6.1 |

有关 MK2069-01 的资源

描述

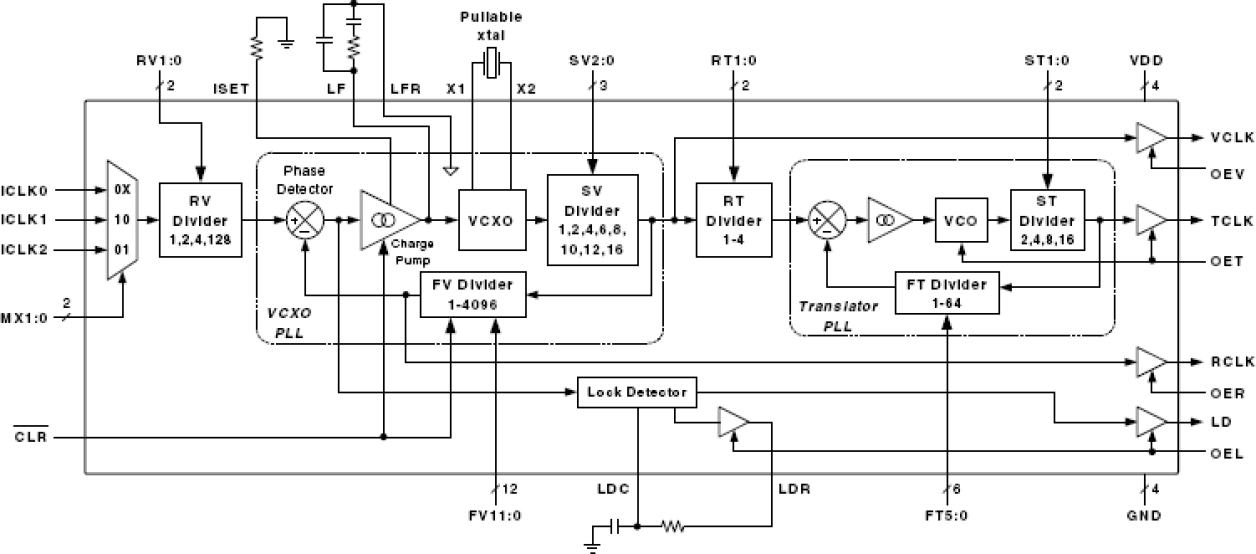

The MK2069-01 is a VCXO (Voltage Controlled Crystal Oscillator) based clock generator that offers system synchronization, jitter attenuation, and frequency multiplication or translation. It can accept an unstable, jittery input clock and provide a de-jittered, low phase noise output clock at a user determined frequency. The device's clock multiplication ratios are user selectable since all major PLL divider blocks can be configured through device pin settings. External PLL loop filter components allow tailoring of the VCXO PLL loop response and therefore the clock jitter attenuation characteristics. The MK2069-01 is ideal for line card applications. Its three input MUX enables selection of the master or slave (backup) system clocks, as well as a backup local line card clock. The lock detector (LD) output serves as a clock status monitor. The clear (CLR) input enables rapid synchronization to the phase of a newly selected input clock, while eliminating the generation of extra clock cycles and wander caused by memory in the PLL feedback divider. CLR also serves as a temporary holdover function when kept low.