封装信息

| CAD 模型: | View CAD Model |

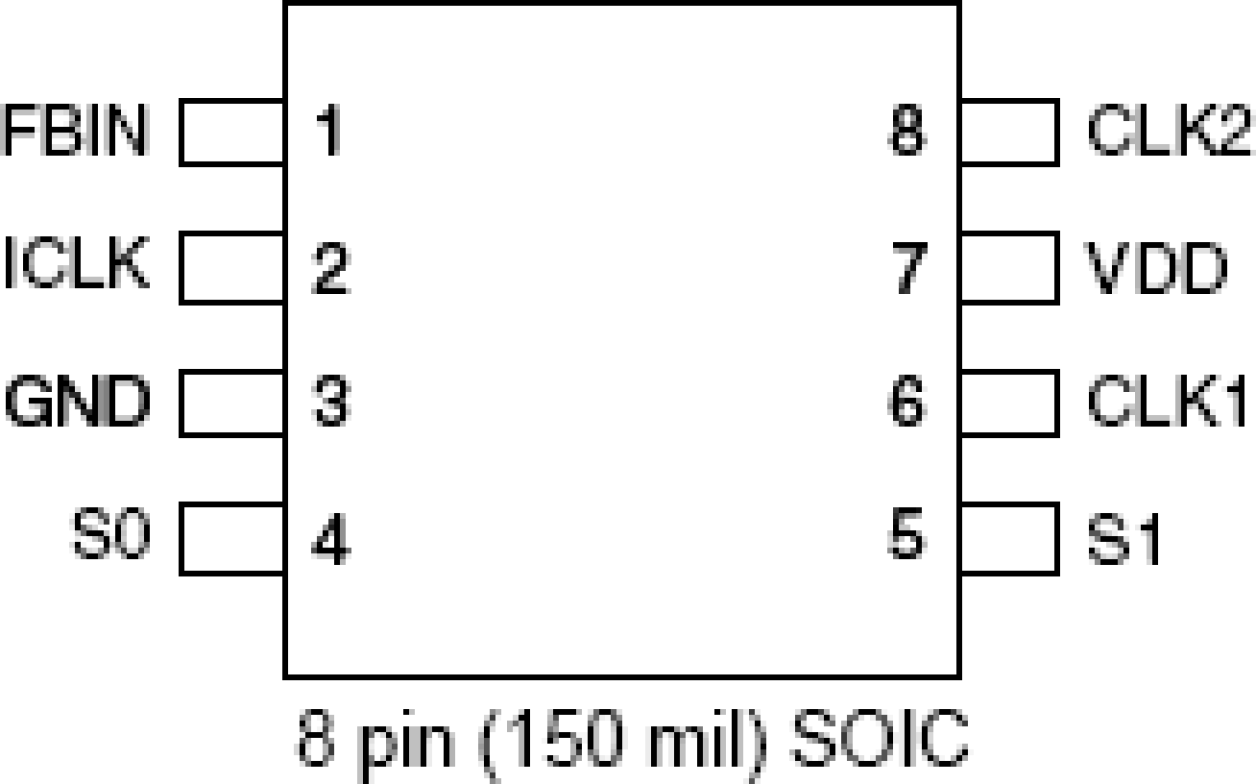

| Pkg. Type: | SOIC |

| Pkg. Code: | DCG8 |

| Lead Count (#): | 8 |

| Pkg. Dimensions (mm): | 4.9 x 3.9 x 1.5 |

| Pitch (mm): | 1.27 |

环境和出口类别

| Moisture Sensitivity Level (MSL) | 1 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

产品属性

| Lead Count (#) | 8 |

| Carrier Type | Reel |

| Moisture Sensitivity Level (MSL) | 1 |

| Advanced Features | Reference Output |

| Input Freq (MHz) | 0.31 - 168 |

| Output Voltage (V) | 3.3 |

| Qty. per Reel (#) | 3000 |

| Qty. per Carrier (#) | 0 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range (°C) | 0 to 70°C |

| Accepts Spread Spec Input | No |

| Core Voltage (V) | 3.3V, 5V |

| Length (mm) | 4.9 |

| MOQ | 3000 |

| Output Freq Range (MHz) | 10 - 168 |

| Output Type | LVCMOS |

| Outputs (#) | 2 |

| Package Area (mm²) | 19.1 |

| Pitch (mm) | 1.27 |

| Pkg. Dimensions (mm) | 4.9 x 3.9 x 1.5 |

| Pkg. Type | SOIC |

| Product Category | Zero Delay Buffers |

| Reel Size (in) | 13 |

| Reference Output | Yes |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Spread Spectrum | No |

| Tape & Reel | Yes |

| Thickness (mm) | 1.5 |

| Width (mm) | 3.9 |

有关 MK2302-01 的资源

描述

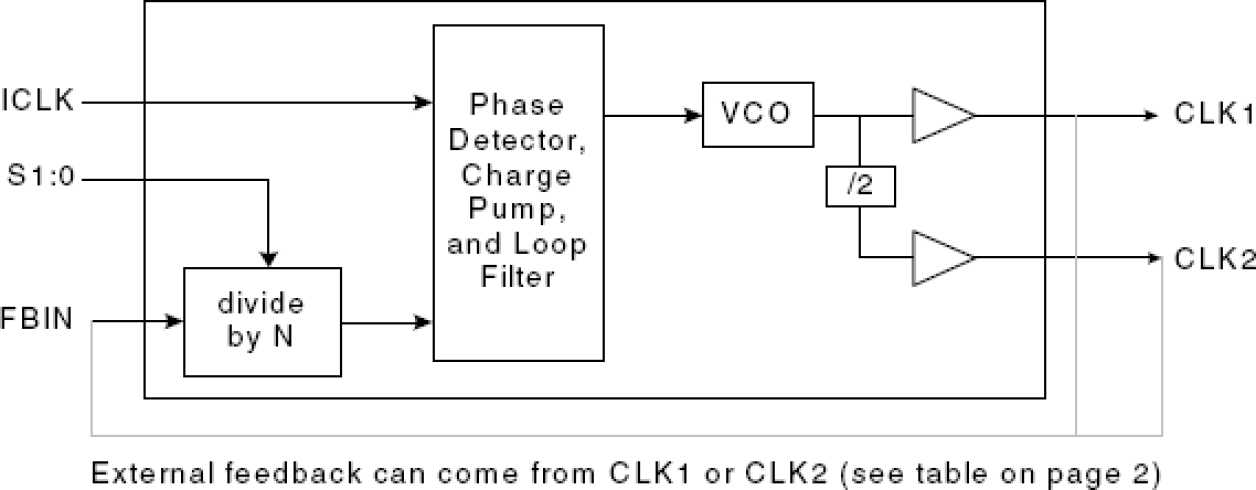

The MK2302-01 is a high-performance Zero Delay Buffer (ZDB) that integrates Renesas' proprietary analog/digital Phase-Locked Loop (PLL) techniques. The chip is part of Renesas' ClockBlocks™ family and was designed as a performance upgrade to meet today's higher speed and lower voltage requirements. The zero delay feature means that the rising edge of the input clock aligns with the rising edges of both output clocks, giving the appearance of no delay through the device. There are two outputs on the chip, one being a low-skew divide by two of the other output. The MK2302-01 is ideal for synchronizing outputs in a large variety of systems, from personal computers to data communications to graphics/video. By allowing off-chip feedback paths, the device can eliminate the delay through other devices.