特性

- 超低相位噪声合成器: 4MHz 高通滤波(HPF)条件下, 12kHz 到 20MHz的RMS jitter低于 18fs

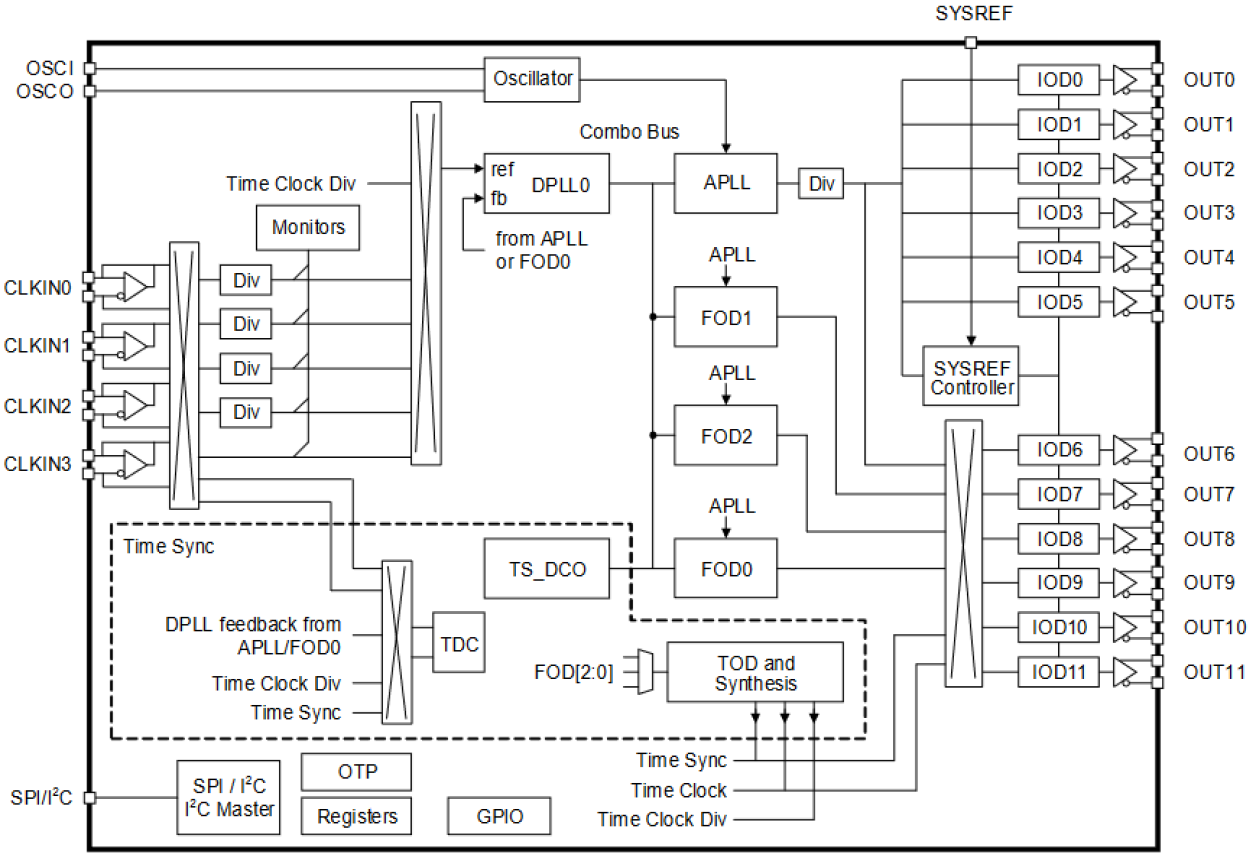

- 独立同步域:三个独立的低相位噪声同步域

- 频域:四个独立的低相位噪声频域

- 协议支持:兼容 JESD204B/C 标准

- 时间同步功能:配备时间数字转换器 (TDC)、time of day (TOD) 计数器和精确时间同步协议 (PTP) 时钟

- 时钟输出:12 个时钟输出,带独立整数分频器

- 8 个输出,使用 LVDS、HCSL (AC-LVPECL) 或 CML

- 4路输出,使用 LVDS、HCSL (AC-LVPECL) 或 LVCMOS

- 输出频率范围

- CML:DC to 2.5GHz

- LVDS 或 HCSL:DC to 1GHz

- LVCOMS:DC to 250MHz

- 输入时钟规格

- 时钟输入:4 个差分或单端时钟输入

- 电压容忍度:当器件断电时,时钟输入可容忍 1.8V 输入,灌电流小于 1mA

- 输入频率范围:CLKIN输入频率范围:DC to 1GHz

- 时间同步 TDC:支持 1PPS(秒脉冲)和 PP2S 输入

- 数字锁相环 (DPLL)

- 符合 ITU-T G.8262 和 G.8262.1 标准

- 输入到输出相位变化 ≤ 100ps

- 数控振荡器 (DCO):频率分辨率 < 10^-13

- 工作电压:在 1.8V 电源下工作

- 封装:紧凑的 9mm x 9mm 尺寸,采用 100 引脚 BGA 封装

描述

RC38112 是一款超低相位噪声射频同步器、多频时钟合成器和数控振荡器 (DCO)。 它为 5G 射频单元 (RU)、分布单元 (DU) 以及网络交换机和路由器提供卓越的性能。 它能够输出具有超低带内相位噪声和超低杂散电平的时钟,从而提高了 4G 和 5G 射频收发器的可靠性和效率。 该器件为参考时钟提供了最大裕量的抖动性能,具有多达三个同步域和四个频率域,使设计人员能够简化其整体 PCB 设计,并提供单芯片时钟解决方案,完美支持 CPRI 或 eCPRI 和射频的时钟需求。 它提供低功耗和更小的面积,同时仍能实现超低抖动,并维持 5G 和 5G-A BTS 射频单元设计所必需的超低相位相干性。 RC38112 允许灵活的选择锁定到外部参考时钟或自由运行的晶体/振荡器,并具备无损伤的参考源切换功能,即在冗余时钟源之间切换时也能确保不中断业务,使其成为确保电信应用中稳健、精确定时和相位控制的理想选择。

此为出厂可配置设备。

试用自定义部件配置工具。

试用自定义部件配置工具。

产品参数

| 属性 | 值 |

|---|---|

| Outputs (#) | 12 |

| Output Type | HCSL, LVCMOS, LVDS |

| Output Freq Range (MHz) | 5.0E-7 - 1000 |

| Input Freq (MHz) | 5.0E-7 - 1000 |

| Inputs (#) | 8 |

| Input Type | CML, Crystal, HCSL, LVCMOS, LVDS, LVPECL |

| Output Banks (#) | 12 |

| Core Voltage (V) | 1.8V, 3.3V |

| Output Voltage (V) | 1.8 |

| Product Category | FemtoClock 3 |

封装选项

| Pkg. Type | Pkg. Dimensions (mm) | Lead Count (#) | Pitch (mm) |

|---|---|---|---|

| CABGA | 9.0 x 9.0 x 1.1 | 100 | 0.8 |

应用

- 5G 射频单元 (RU)

- 5G 分布单元 (DU)、交换机和路由器

- 用于 112Gbps 和 224Gbps SerDes 的参考时钟

- 高性能 DCO,适用于基于精准时间同步协议 (PTP) 的时钟

- 数据中心交换机、加速卡、AI 互连