特性

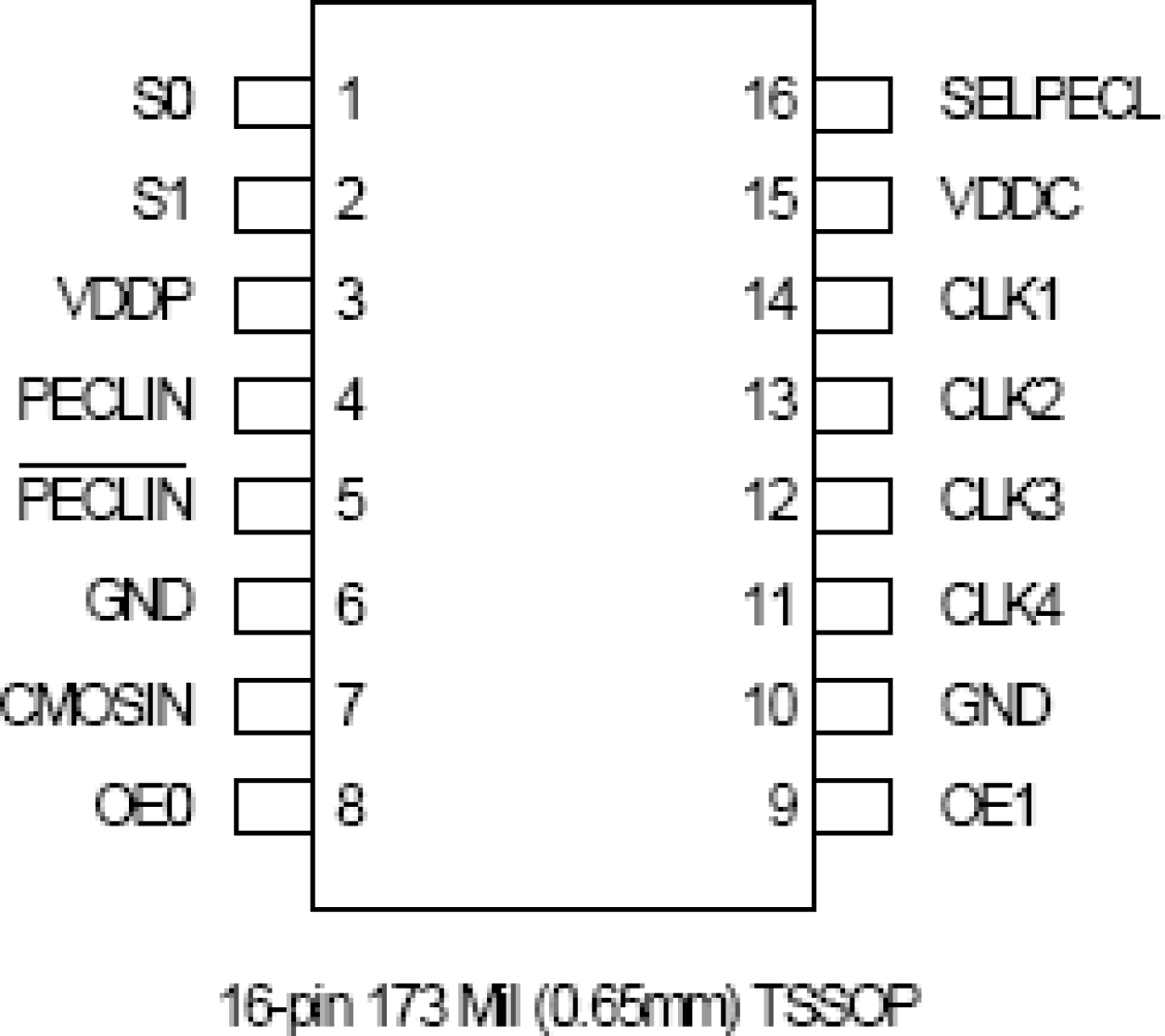

- 16-pin TSSOP package

- Pb (lead) free package

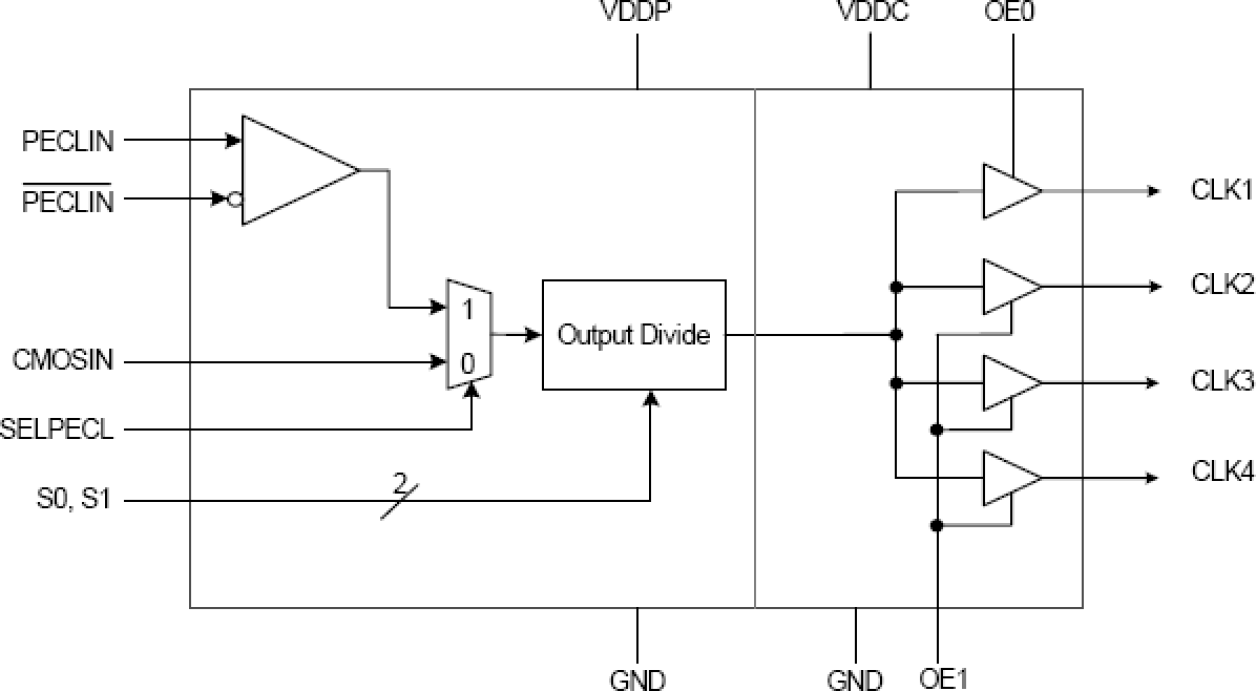

- Selectable PECL or CMOS inputs

- Operates up to 250 MHz

- Works as a voltage translator

- Four low skew (<250 ps) outputs

- Selectable internal divider

- Operating input voltages of 3.3 V or 5.0 V

- Operating output voltages of 2.5 V, 3.3 V or 5.0 V

- Ideal for IA64 designs

描述

The 558-01 accepts a high speed input of either PECL or CMOS, integrates a divider of 1, 2, 3, or 4, and provides four CMOS low skew outputs. The chip also has output enables so that one, three, or all four outputs can be tri-stated. The 558-01 is a member of the IDT Clock Blocks™ family of clock generation, synchronization, and distribution devices.

当前筛选条件