封装信息

| CAD 模型: | View CAD Model |

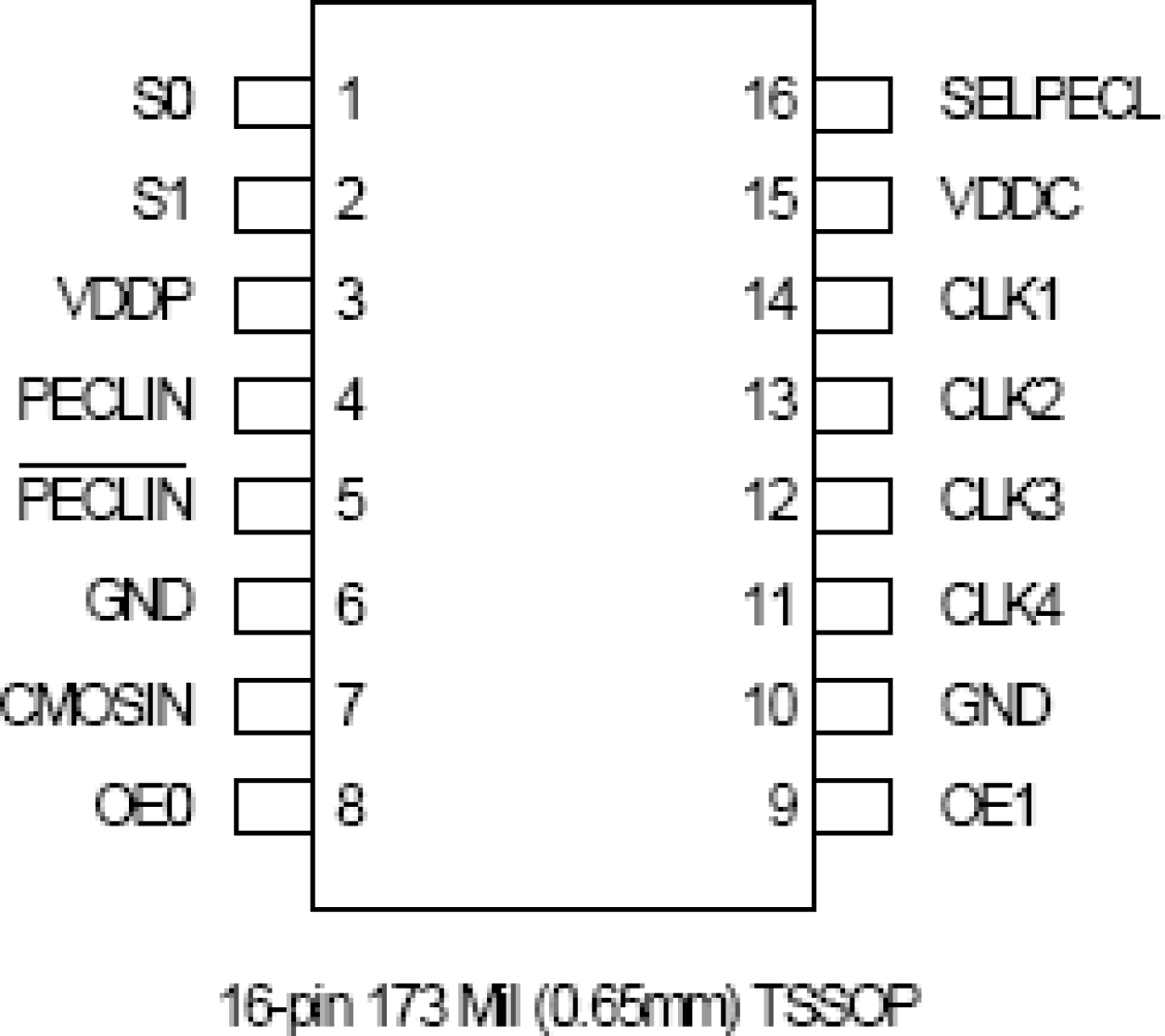

| Pkg. Type: | TSSOP |

| Pkg. Code: | PGG16 |

| Lead Count (#): | 16 |

| Pkg. Dimensions (mm): | 5.0 x 4.4 x 1.0 |

| Pitch (mm): | 0.65 |

环境和出口类别

| Moisture Sensitivity Level (MSL) | 1 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

产品属性

| Lead Count (#) | 16 |

| Carrier Type | Reel |

| Moisture Sensitivity Level (MSL) | 1 |

| Qty. per Reel (#) | 2500 |

| Qty. per Carrier (#) | 0 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range (°C) | 0 to 70°C |

| Core Voltage (V) | 3.3V, 5V |

| Divider Value | 1, 2, 3, 4 |

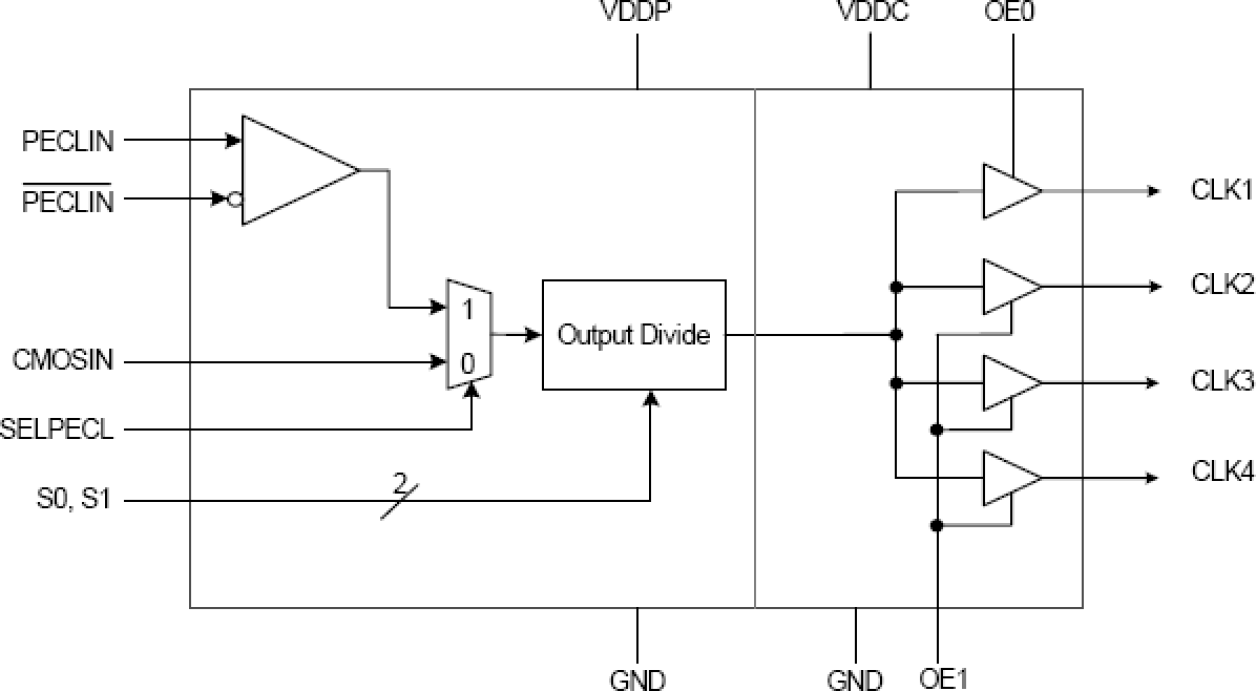

| Function | Buffer, Multiplexer, Divider |

| Input Freq (MHz) | 250 |

| Input Type | LVCMOS, LVPECL |

| Inputs (#) | 2 |

| Length (mm) | 5 |

| MOQ | 2500 |

| Output Banks (#) | 2 |

| Output Freq Range (MHz) | 250 |

| Output Skew (ps) | 250 |

| Output Type | LVCMOS |

| Output Voltage (V) | 2.5V, 3.3V, 5V |

| Outputs (#) | 4 |

| Package Area (mm²) | 22 |

| Pitch (mm) | 0.65 |

| Pkg. Dimensions (mm) | 5.0 x 4.4 x 1.0 |

| Pkg. Type | TSSOP |

| Product Category | Clock Buffers & Drivers, Clock Dividers, Clock Multiplexers |

| Reel Size (in) | 13 |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Tape & Reel | Yes |

| Thickness (mm) | 1 |

| Width (mm) | 4.4 |

有关 558-01 的资源

描述

The 558-01 accepts a high speed input of either PECL or CMOS, integrates a divider of 1, 2, 3, or 4, and provides four CMOS low skew outputs. The chip also has output enables so that one, three, or all four outputs can be tri-stated. The 558-01 is a member of the IDT Clock Blocks™ family of clock generation, synchronization, and distribution devices.