特性

- Dual-Port allows simultaneous access of the same memory location

- RapidWrite Mode simplifies high-speed consecutive write cycles

- Dual chip enables allow for depth expansion without external logic

- Easily expands data bus width to 72 bits or more using the Master/Slave select when cascading more than one device

- Busy and Interrupt Flags

- On-chip port arbitration logic

- Full on-chip hardware support of semaphore signaling between ports

- Fully asynchronous operation from either port

- Separate byte controls for multiplexed bus and bus matching compatibility

- Sleep Mode Inputs on both ports

- Includes JTAG functionality

- Single 2.5V (±100mV) power supply for core

- LVTTL-compatible, selectable 3.3V (±150mV)/2.5V (±100mV) power supply for I/Os and control signals on each port

- Available in a 256-ball BGA, 208-pin PQFP and 208-ball fpBGA.

- Industrial temperature range (–40C to +85C) is available

描述

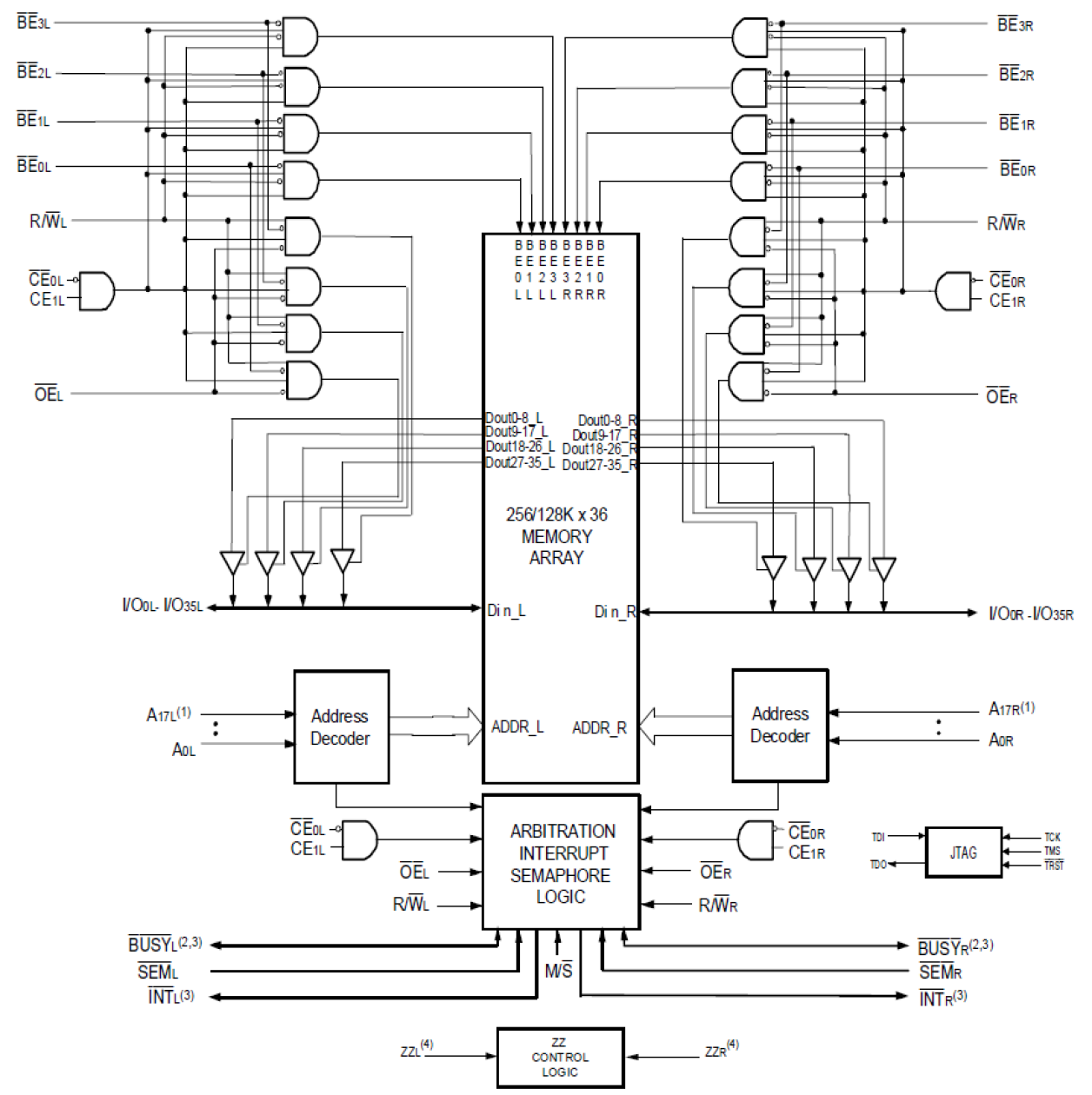

The 70T651 is a high-speed 256K x 36 Asynchronous Dual-Port Static RAM designed to be used as a stand-alone Dual-Port RAM or as a combination MASTER/ SLAVE Dual-Port RAM for 72-bit-or-more word system which would result in full-speed, error-free operation without the need for additional discrete logic. An automatic power down feature controlled by the chip enables (either CE0 or CE1) permit the on-chip circuitry of each port to enter a very low standby power mode.

产品参数

| 属性 | 值 |

|---|---|

| Core Voltage (V) | 2.5 |

| Bus Width (bits) | 36 |

| Density (Kb) | 9216 |

| Pkg. Code | BC256, BF208 |

| Interface | Async |

| I/O Type | 2.5 V LVTTL, 3.3 V LVTTL |

| Access Time (ns) | 10, 12 |

| Temp. Range (°C) | -40 to 85°C |

| Architecture | Dual-Port |

| Organization | 256K x 36 |

| Function | Busy, Interrupt, JTAG, Master, Semaphore, Slave, Sleep Mode |

当前筛选条件