特性

- Supports high performance system speed - 100 MHz (7.5 ns Clock-to-Data Access)

- ZBTTM Feature - No dead cycles between write and read cycles

- Internally synchronized output buffer enable eliminates the need to control OE

- Single R/W (READ/WRITE) control pin

- 4-word burst capability (Interleaved or linear)

- Individual byte write (BW1 - BW4) control (May tie active)

- Three chip enables for simple depth expansion

- 2.5V power supply (±5%)

- 2.5V (±5%) I/O Supply (VDDQ)

- Power down controlled by ZZ input

- Boundary Scan JTAG Interface (IEEE 1149.1 Compliant)

- Available in 100-pin TQFP and 119-pin BGA packages

描述

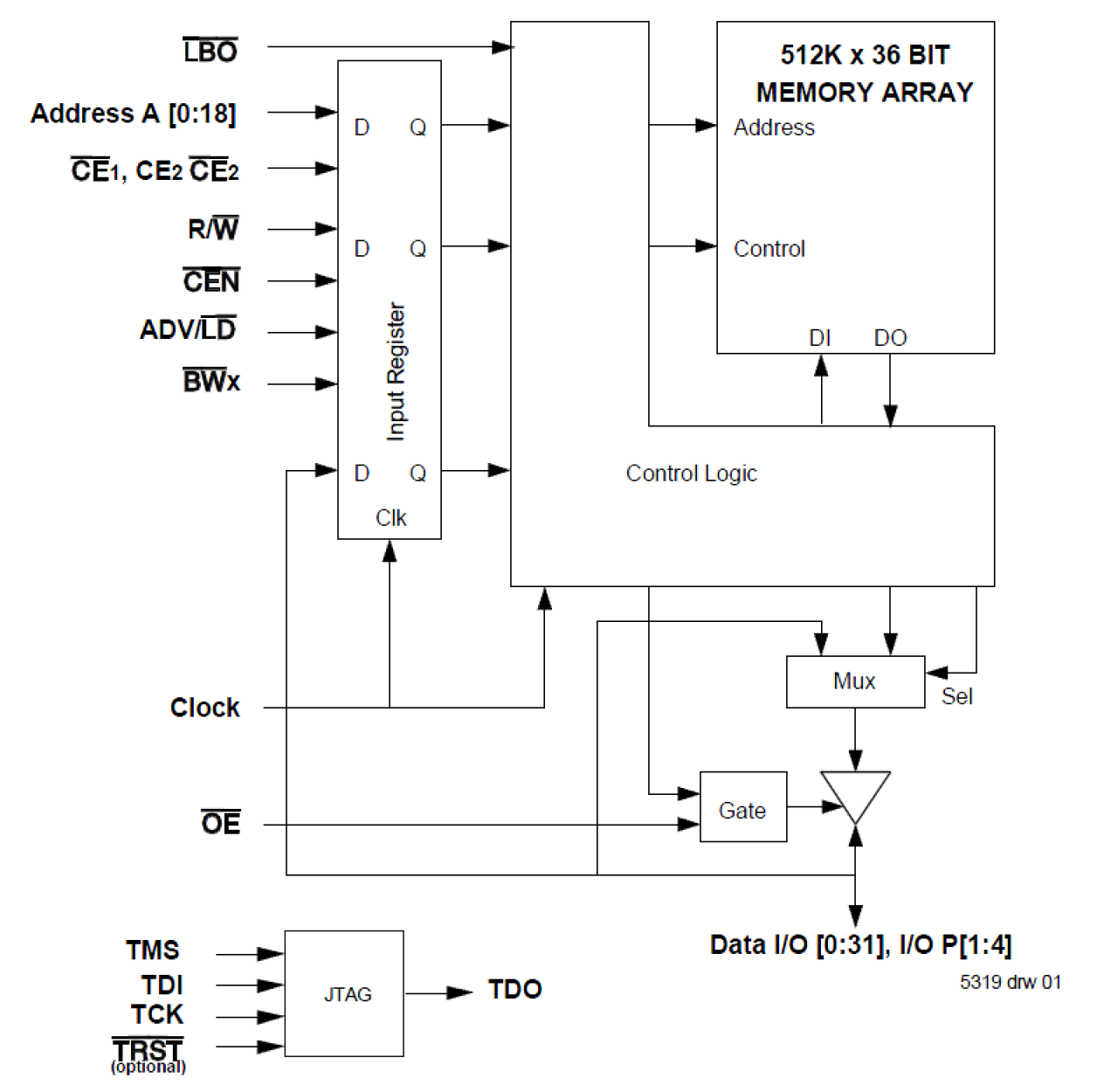

The 71T75902 2.5V CMOS Synchronous SRAM organized as 1M x 18 (18 Megabit). It is designed to eliminate dead bus cycles when turning the bus around between reads and writes, or writes and reads. Thus it has been given the name ZBTTM, or Zero Bus Turnaround.

产品参数

| 属性 | 值 |

|---|---|

| Density (Kb) | 18432 |

| Bus Width (bits) | 18 |

| Core Voltage (V) | 2.5 |

| Pkg. Code | PKG100 |

| Organization | 1024K x 18 |

| I/O Voltage (V) | 2.5 - 2.5 |

| Temp. Range (°C) | -40 to 85°C |

| Architecture | ZBT |

| Output Type | Flowthrough |

封装选项

| Pkg. Type | Pkg. Dimensions (mm) | Lead Count (#) | Pitch (mm) |

|---|---|---|---|

| TQFP | 20.0 x 14.0 x 1.4 | 100 | 0.65 |

当前筛选条件