封装信息

| CAD 模型: | View CAD Model |

| Pkg. Type: | TQFP |

| Pkg. Code: | PKG100 |

| Lead Count (#): | 100 |

| Pkg. Dimensions (mm): | 20.0 x 14.0 x 1.4 |

| Pitch (mm): | 0.65 |

环境和出口类别

| Pb (Lead) Free | Yes |

| Moisture Sensitivity Level (MSL) | 3 |

| ECCN (US) | 3A991.b.2.a |

| HTS (US) | 8542.32.0041 |

产品属性

| Lead Count (#) | 100 |

| Pb (Lead) Free | Yes |

| Carrier Type | Tray |

| Moisture Sensitivity Level (MSL) | 3 |

| Architecture | ZBT |

| Bus Width (bits) | 36 |

| Core Voltage (V) | 3.3 |

| Density (Kb) | 4608 |

| I/O Frequency (MHz) | 133 - 133 |

| I/O Voltage (V) | 2.5 - 2.5 |

| Length (mm) | 20 |

| MOQ | 144 |

| Organization | 128K x 36 |

| Output Type | Pipelined |

| Package Area (mm²) | 280 |

| Pb Free Category | e3 Sn |

| Pitch (mm) | 0.65 |

| Pkg. Dimensions (mm) | 20.0 x 14.0 x 1.4 |

| Pkg. Type | TQFP |

| Price (USD) | $7.26333 |

| Qty. per Carrier (#) | 72 |

| Qty. per Reel (#) | 0 |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Tape & Reel | No |

| Temp. Range (°C) | 0 to 70°C |

| Thickness (mm) | 1.4 |

| Width (mm) | 14 |

| 已发布 | No |

有关 71V3556 的资源

描述

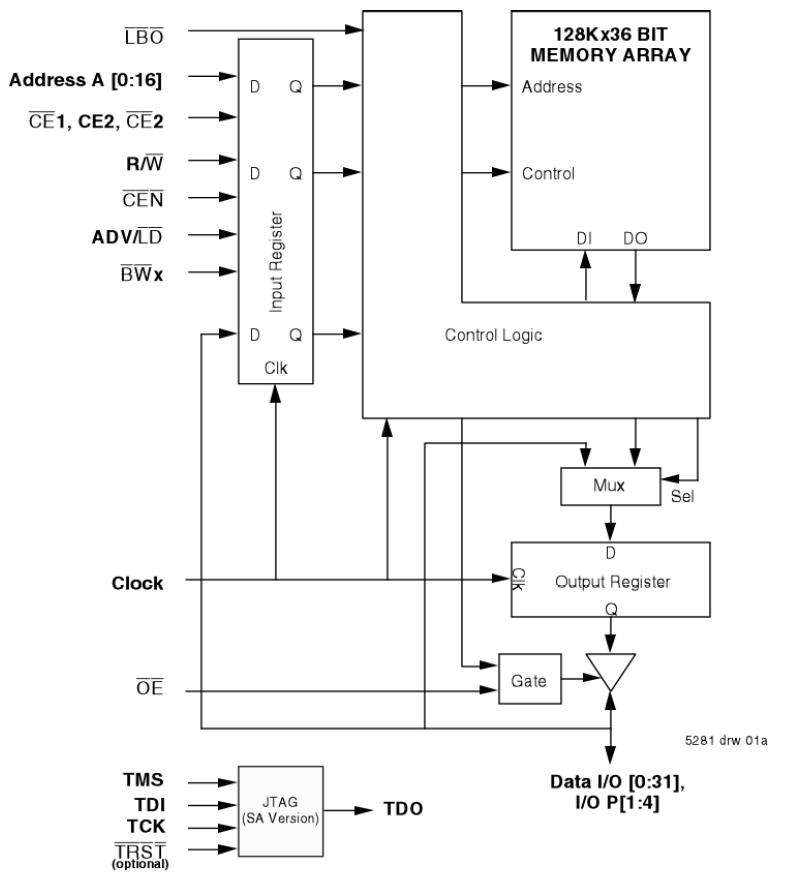

The 71V3556 3.3V CMOS synchronous SRAM, organized as 128K x 36, is designed to eliminate dead bus cycles when turning the bus around between reads and writes or writes and reads. Thus, it has been given the name ZBT™, or Zero Bus Turnaround. The 71V3556 contains data I/O, address, and control signal registers.