特性

- Fast access times 7.5ns up to 117MHz clock frequency

- LBO input selects interleaved or linear burst mode

- Self-timed write cycle with global write control (GW), byte write

- enable (BWE), and byte writes (BWx)

- 3.3V core power supply

- Power down controlled by ZZ input

- 3.3V I/O supply (VDDQ)

- Available in 100-pin TQFP, 119-pin BGA and 165 fpBGA packages

描述

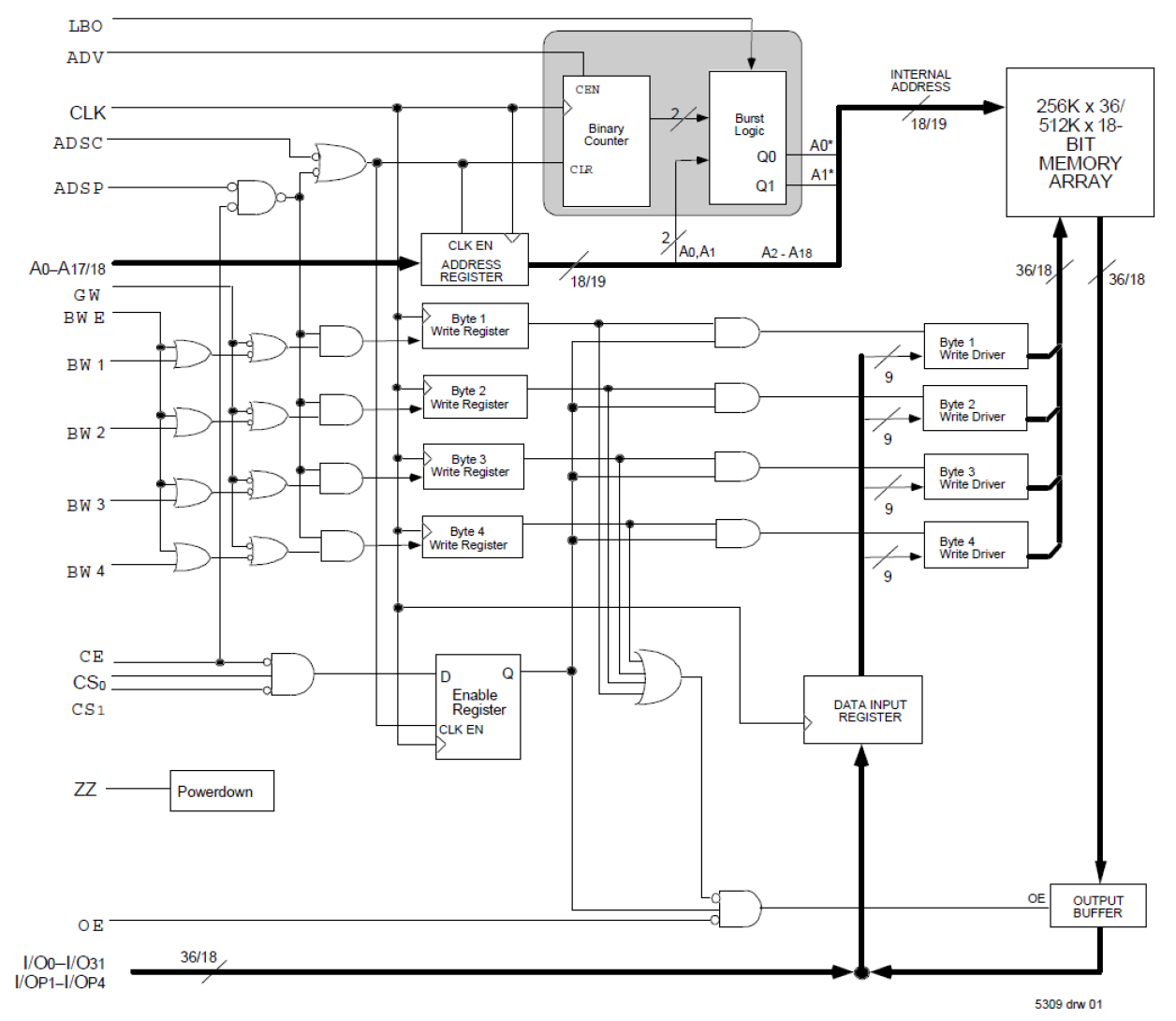

The 71V67703 3.3V CMOS SRAM is organized as 256K x 36. The 71V67703 SRAM contains write, data, address and control registers. There are no registers in the data output path (flow-through architecture). The burst mode feature offers the highest level of performance to the system designer, as it can provide four cycles of data for a single address presented to the SRAM.

产品参数

| 属性 | 值 |

|---|---|

| Density (Kb) | 9216 |

| Bus Width (bits) | 36 |

| Core Voltage (V) | 3.3 |

| Pkg. Code | BQ165, PKG100 |

| Organization | 256K x 36 |

| I/O Voltage (V) | 3.3 - 3.3 |

| Temp. Range (°C) | -40 to 85°C |

| Architecture | Synch Burst |

| Output Type | Flowthrough |

当前筛选条件