封装信息

| CAD 模型: | View CAD Model |

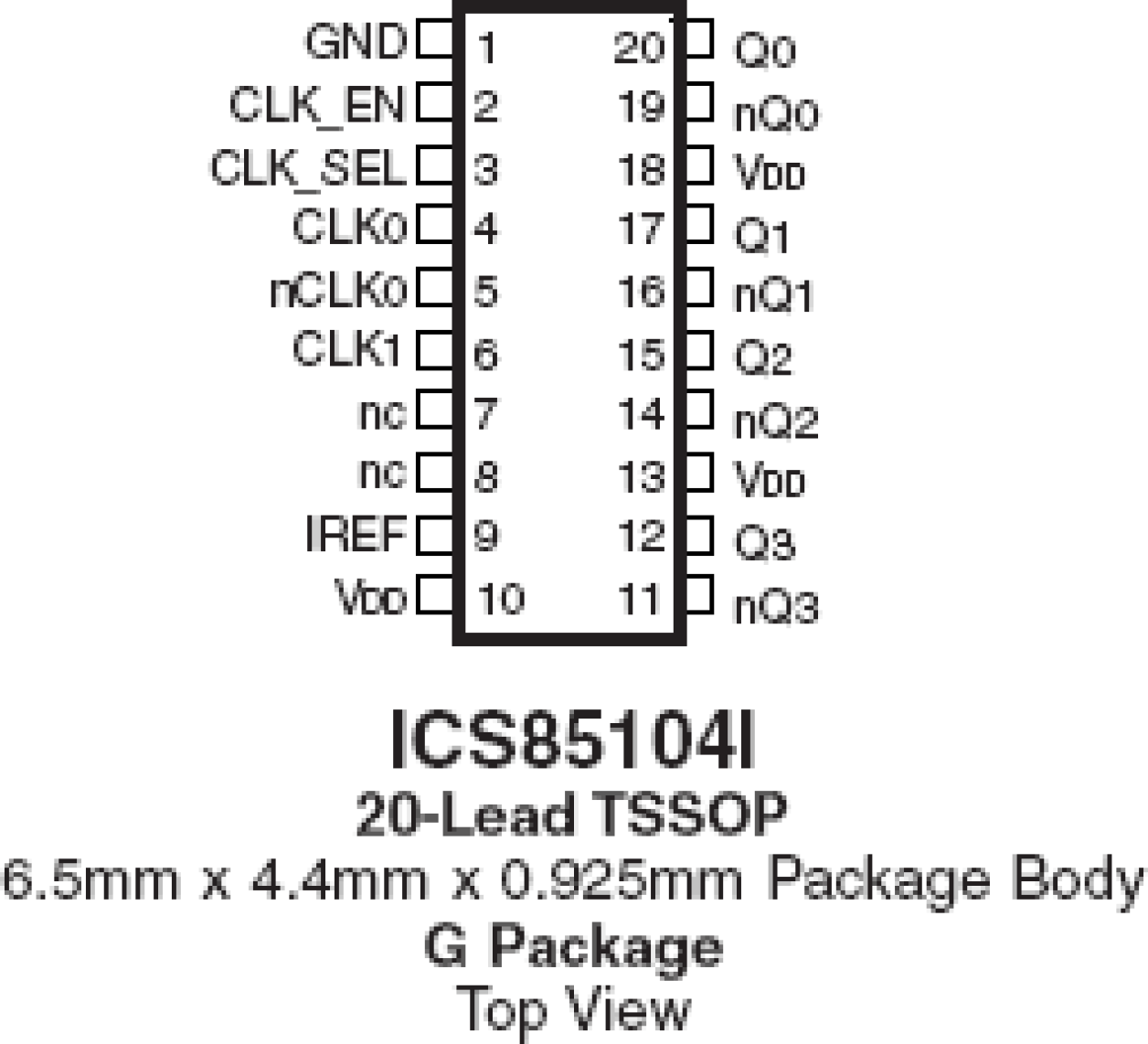

| Pkg. Type: | TSSOP |

| Pkg. Code: | PGG20 |

| Lead Count (#): | 20 |

| Pkg. Dimensions (mm): | 6.5 x 4.4 x 1.0 |

| Pitch (mm): | 0.65 |

环境和出口类别

| Moisture Sensitivity Level (MSL) | 1 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

产品属性

| Lead Count (#) | 20 |

| Carrier Type | Reel |

| Moisture Sensitivity Level (MSL) | 1 |

| Qty. per Reel (#) | 3000 |

| Qty. per Carrier (#) | 0 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range (°C) | -40 to 85°C |

| Additive Phase Jitter Typ RMS (fs) | 220 |

| Additive Phase Jitter Typ RMS (ps) | 0.22 |

| Core Voltage (V) | 3.3 |

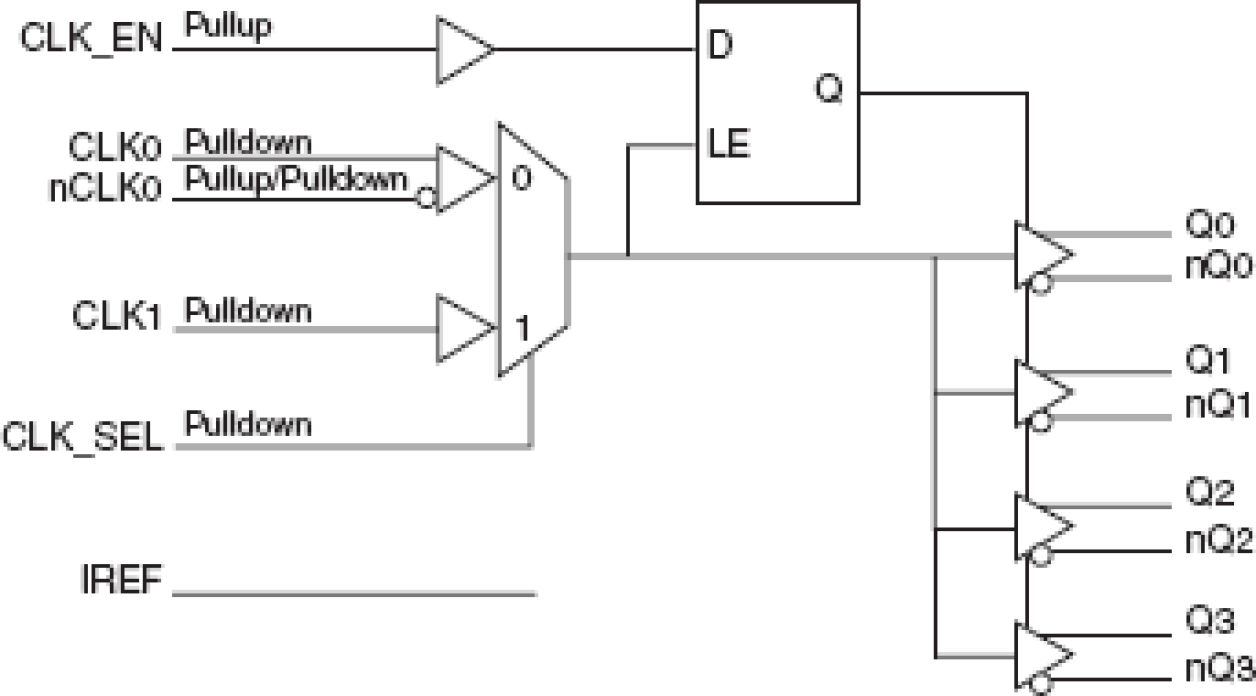

| Function | Buffer, Multiplexer |

| Input Freq (MHz) | 500 |

| Input Type | HCSL, HSTL, LVCMOS, LVDS, LVPECL |

| Inputs (#) | 2 |

| Length (mm) | 6.5 |

| MOQ | 3000 |

| Output Banks (#) | 1 |

| Output Freq Range (MHz) | 500 |

| Output Skew (ps) | 100 |

| Output Type | HCSL |

| Output Voltage (V) | 3.3 |

| Outputs (#) | 4 |

| Package Area (mm²) | 28.6 |

| Pitch (mm) | 0.65 |

| Pkg. Dimensions (mm) | 6.5 x 4.4 x 1.0 |

| Pkg. Type | TSSOP |

| Reel Size (in) | 13 |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Tape & Reel | Yes |

| Thickness (mm) | 1 |

| Width (mm) | 4.4 |

| 已发布 | No |

有关 85104I 的资源

描述

The 85104I is a low skew, high performance 1-to-4 Differential/LVCMOS-to-0.7V HCSL Fanout Buffer. The 85104I has two selectable clock inputs. The CLK0, nCLK0 pair can accept most standard differential input levels. The single-ended CLK1 can accept LVCMOS or LVTTL input levels. The clock enable is internally synchronized to eliminate runt clock pulses on the outputs during asynchronous assertion/deassertion of the clock enable pin. Guaranteed output and part-to-part skew characteristics make the 85104I ideal for those applications demanding well defined performance and repeatability.