特性

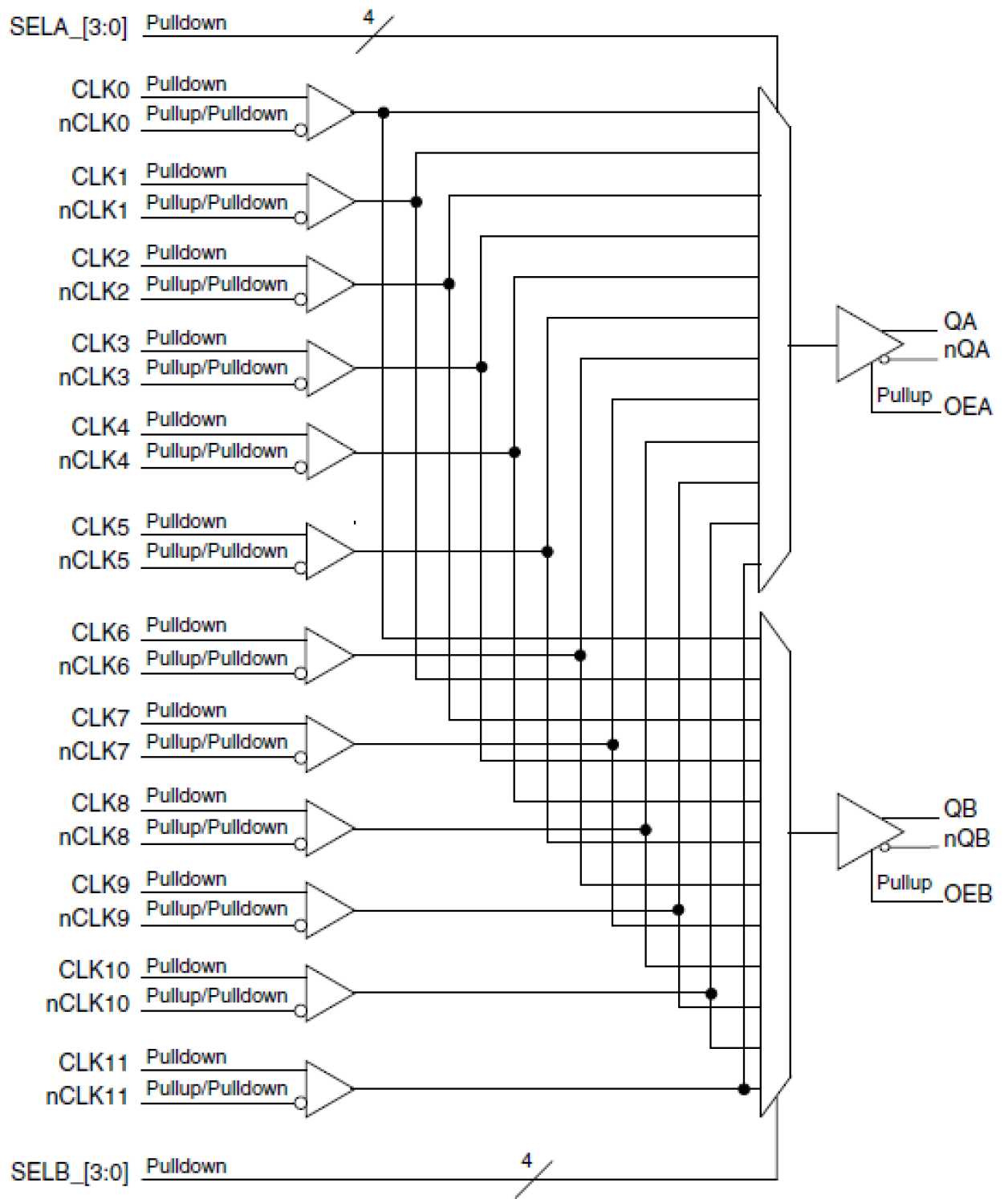

- High speed 12.2 differential multiplexer

- Two differential 3.3V or 2.5V LVPECL outputs

- Maximum output frequency: 3GHz

- Translates any single ended input signal to LVPECL levels with resistor bias on nCLKx input

- Propagation delay: 1.15ns (maximum)

- Input skew: 150ps (maximum)

- Output skew: 50ps (maximum)

- Part-to-part skew: 250ps (maximum)

- Additive phase jitter, RMS: 0.114ps (typical) @ 155.52MHz, 3.3V

- Full 3.3V or 2.5V operating supply mode

- -40°C to 85°C ambient operating temperature

- Lead-free (RoHS 6) packaging

- Twelve selectable differential clock or data inputs

- CLKx, nCLKx pairs can accept the following differential input levels: LVPECL, LVDS

描述

The 853S202I is a 12:2 Differential-to-LVPECL Clock Multiplexer which can operate up to 3GHz. The 853S202I has twelve select-able differential clock inputs, any of which can be independently rout-ed to either of the two LVDS outputs. The CLKx, nCLKx input pairs can accept LVPECL or LVDS levels. The fully differential architecture and low propagation delay make it ideal for use in clock distribution circuits.

产品参数

| 属性 | 值 |

|---|---|

| Temp. Range (°C) | -40 to 85°C |

| Product Category | Clock Multiplexers |

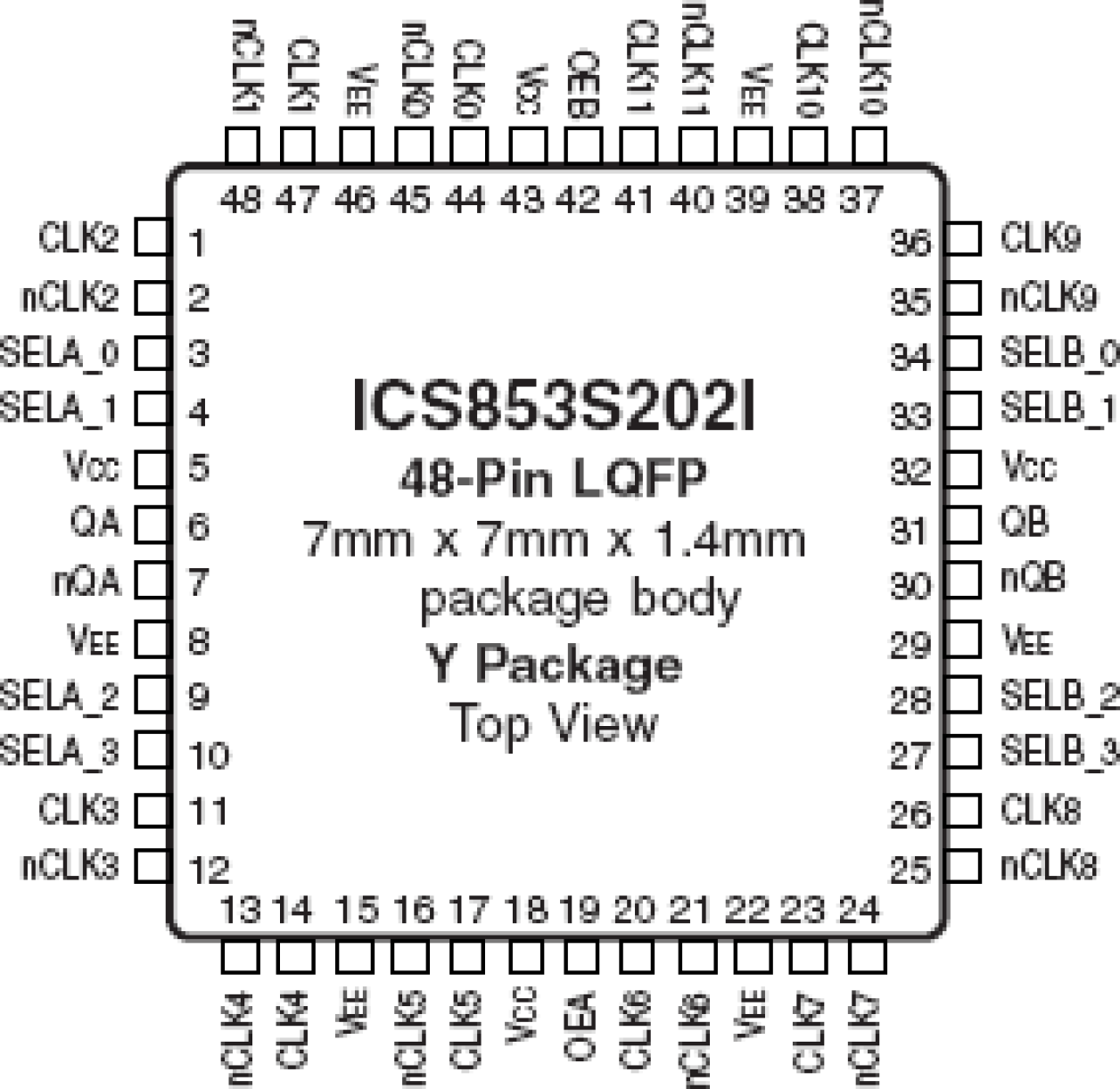

封装选项

| Pkg. Type | Pkg. Dimensions (mm) | Lead Count (#) | Pitch (mm) |

|---|---|---|---|

| TQFP | 7.0 x 7.0 x 1.4 | 48 | 0.5 |

当前筛选条件