封装信息

| CAD 模型: | View CAD Model |

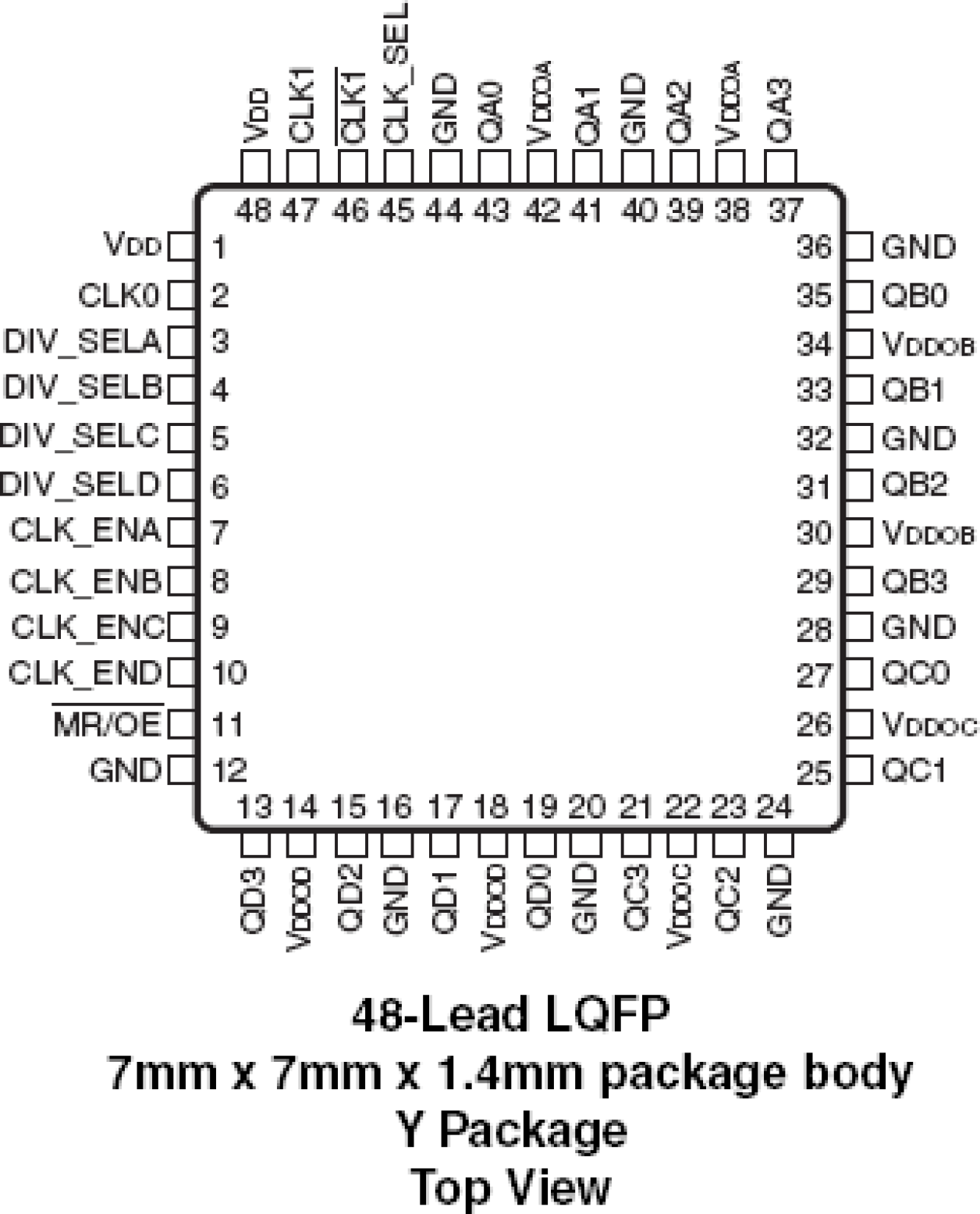

| Pkg. Type: | TQFP |

| Pkg. Code: | PRG48 |

| Lead Count (#): | 48 |

| Pkg. Dimensions (mm): | 7.0 x 7.0 x 1.4 |

| Pitch (mm): | 0.5 |

环境和出口类别

| Moisture Sensitivity Level (MSL) | 3 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

产品属性

| Lead Count (#) | 48 |

| Carrier Type | Reel |

| Moisture Sensitivity Level (MSL) | 3 |

| Qty. per Reel (#) | 2000 |

| Qty. per Carrier (#) | 0 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range (°C) | -40 to 85°C |

| Core Voltage (V) | 2.5V, 3.3V |

| Divider Value | 1, 2 |

| Function | Buffer, Multiplexer |

| Input Freq (MHz) | 250 |

| Input Type | LVCMOS |

| Inputs (#) | 2 |

| Length (mm) | 7 |

| MOQ | 2000 |

| Output Banks (#) | 4 |

| Output Freq Range (MHz) | 250 |

| Output Skew (ps) | 170 |

| Output Type | LVCMOS |

| Output Voltage (V) | 1.8V, 2.5V, 3.3V |

| Outputs (#) | 16 |

| Package Area (mm²) | 49 |

| Pitch (mm) | 0.5 |

| Pkg. Dimensions (mm) | 7.0 x 7.0 x 1.4 |

| Pkg. Type | TQFP |

| Product Category | Clock Buffers & Drivers, Clock Dividers, Clock Multiplexers |

| Reel Size (in) | 13 |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Tape & Reel | Yes |

| Thickness (mm) | 1.4 |

| Width (mm) | 7 |

有关 87016I 的资源

描述

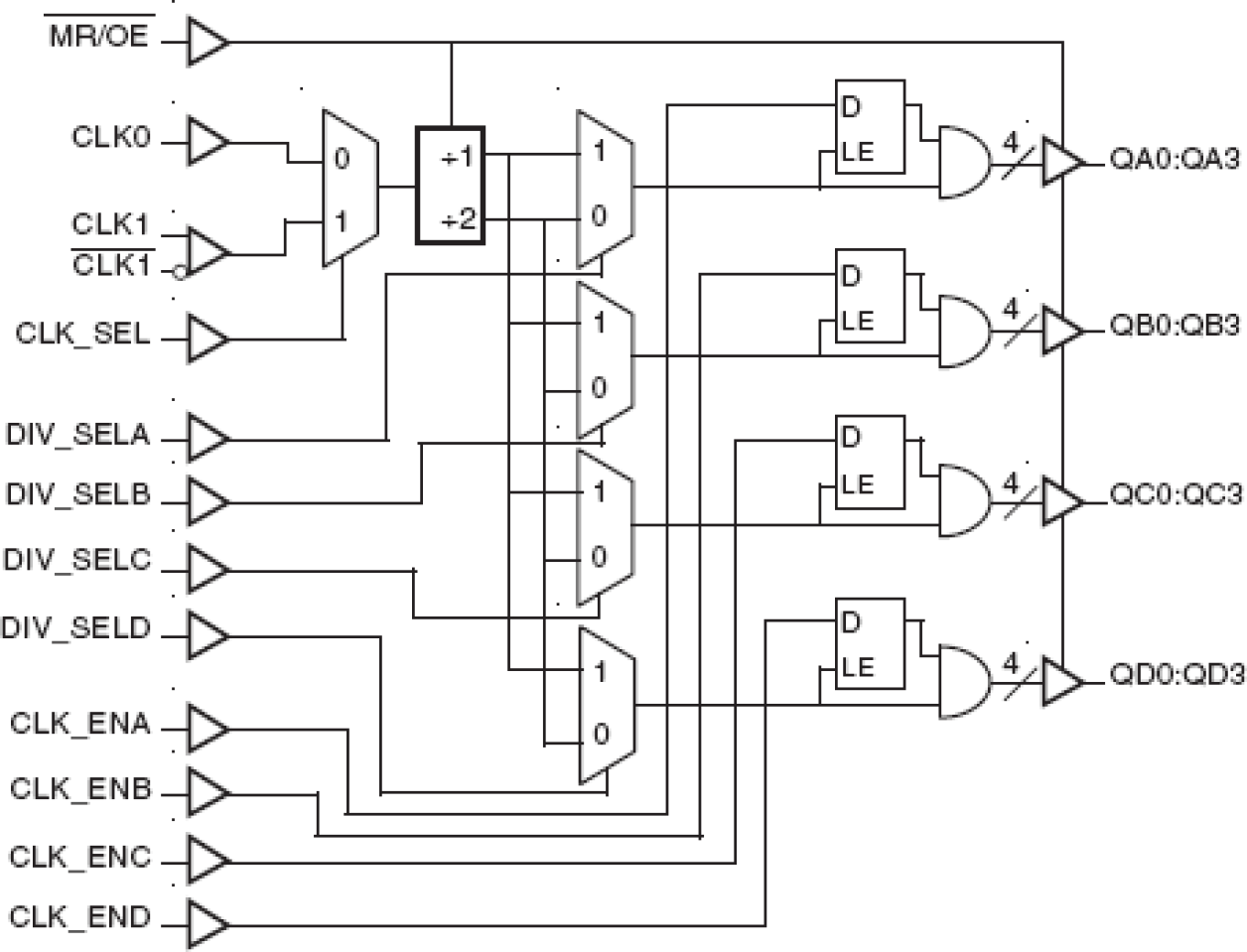

The 87016I is a low skew, 1:16 LVCMOS/LVTTL Clock Generator and is a member of the HiPerClockS family of High Performance Clock Solutions. The device has 4 banks of 4 outputs and each bank can be independently selected for ÷1 or ÷2 frequency operation. Each bank also has its own power supply pins so that the banks can operate at the following different voltage levels: 3.3V, 2.5V, and 1.8V. The low impedance LVCMOS/LVTTL outputs are designed to drive 50? series or parallel terminated transmission lines. The divide select inputs, DIV_SELA:DIV_SELD, control the output frequency of each bank. The output banks can be independently selected for ÷1 or ÷2 operation. The bank enable inputs, CLK_ENA:CLK_END, support enabling and disabling each bank of outputs individually. The CLK_ENA:CLK_END circuitry has a synchronizer to prevent runt pulses when enabling or disabling the clock outputs. The master reset input, MR/OE, resets the ÷1/÷2 flip flops and also controls the active and high impedance states of all outputs. This pin has an internal pull-up resistor and is normally used only for test purposes or in systems which use low power modes. The 87016I is characterized to operate with the core at 3.3V or 2.5V and the banks at 3.3V, 2.5V, or 1.8V. Guaranteed bank, output, and part-to-part skew characteristics make the 87016I ideal for those clock applications demanding well-defined performance and repeatability.