特性

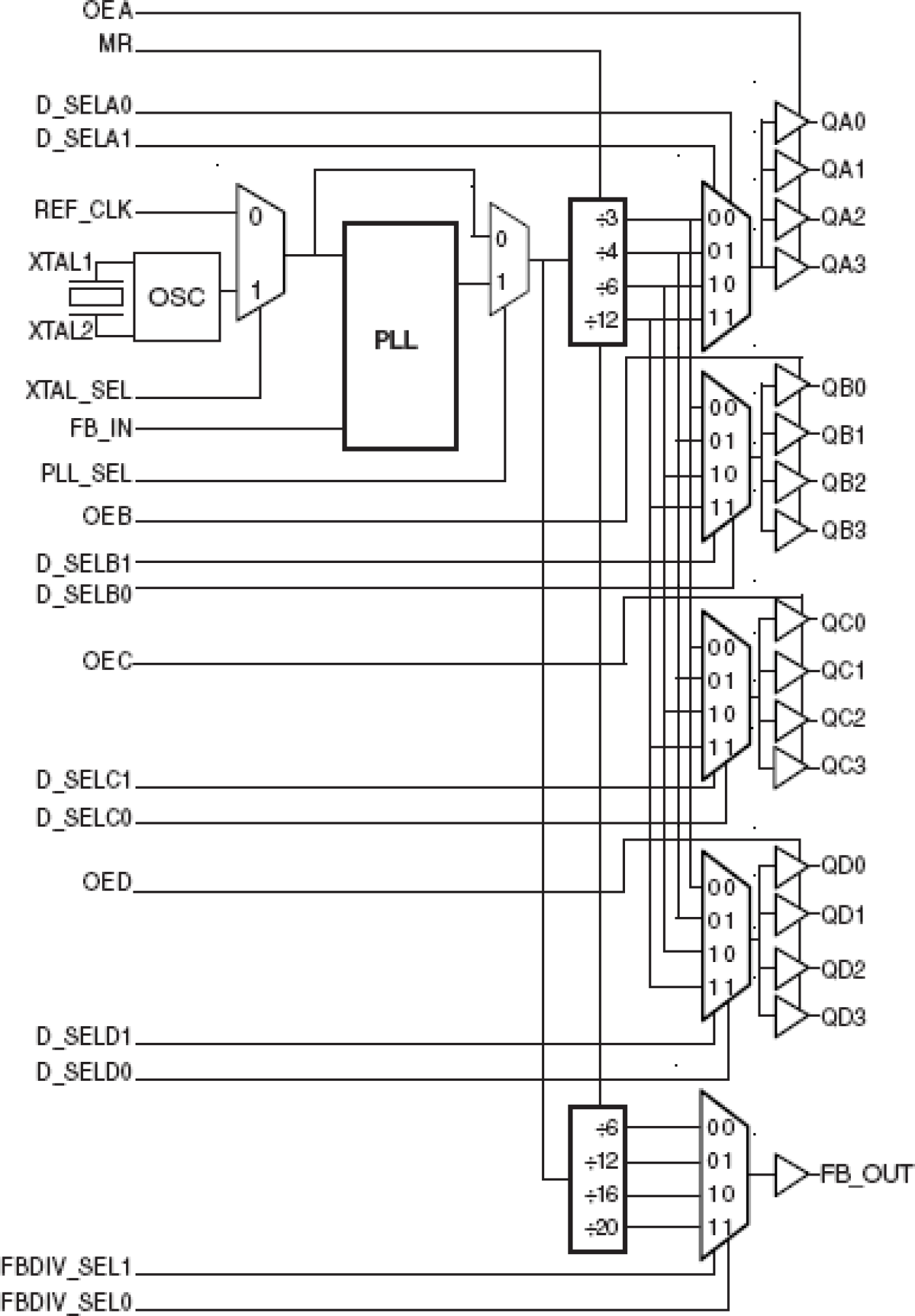

- Fully integrated PLL

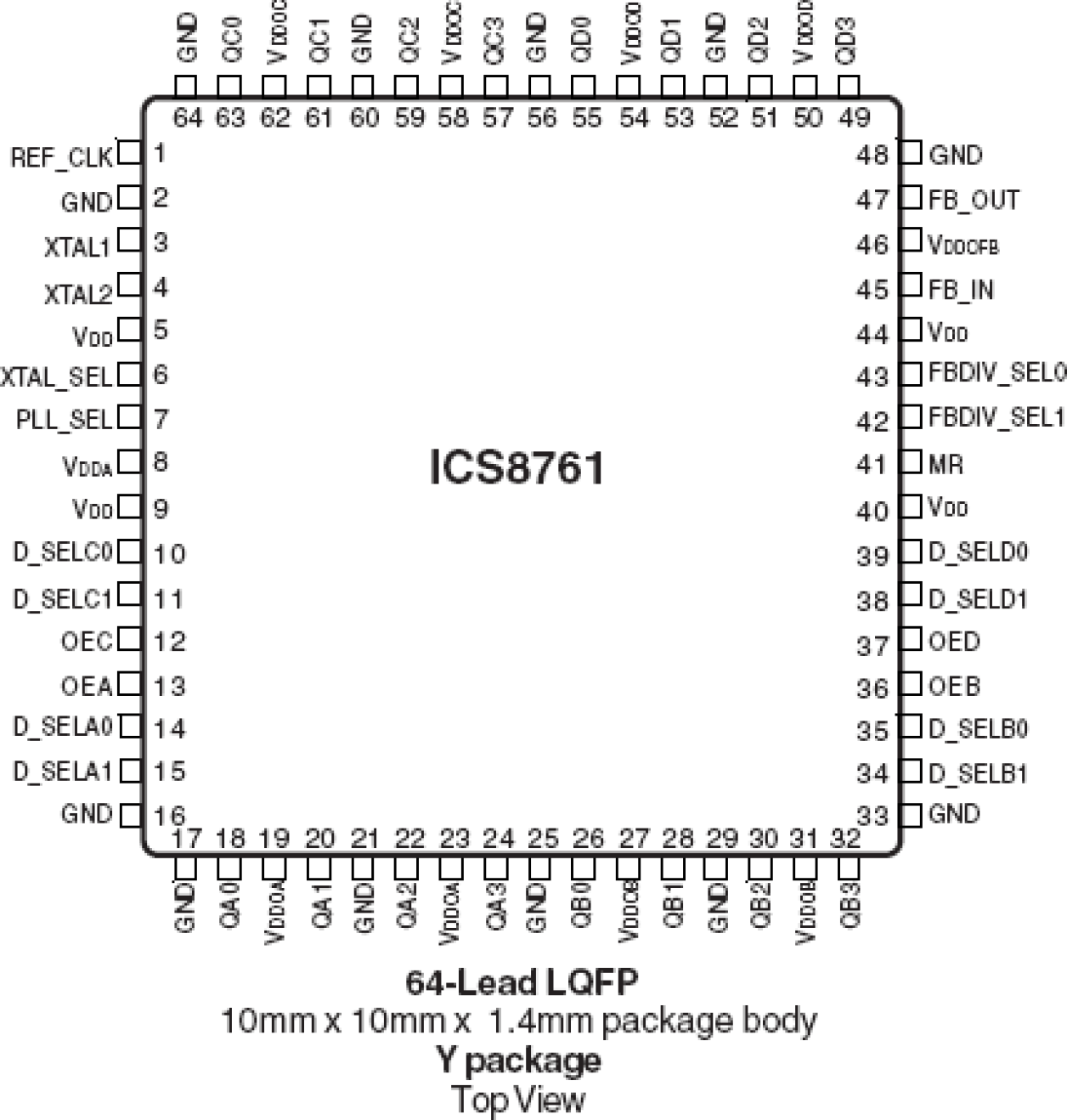

- Seventeen LVCMOS/LVTTL outputs, 15? typical output impedance

- Selectable crystal oscillator interface or LVCMOS/LVTTL REF_CLK

- Maximum output frequency: 166.67MHz

- Maximum crystal input frequency: 38MHz

- Maximum REF_CLK input frequency: 83.33MHz

- Individual banks with selectable output dividers for generating 33.333MHz, 66.66MHz, 100MHz and 133.333MHz simultaneously

- Separate feedback control for generating PCI / PCI-X frequencies from a 20MHz or 25MHz crystal or 33.333MHz or 66.666MHz reference frequency

- Cycle-to-cycle jitter: 70ps (maximum)

- Period jitter, RMS: 17ps (maximum)

- Output skew: 230ps (maximum)

- Bank skew: 40ps (maximum)

- Static phase offset: 0 ± 150ps (maximum)

- Full 3.3V or 3.3V core, 2.5V multiple output supply modes

- 0°C to 85°C ambient operating temperature

- Available in lead-free RoHS-compliant package

描述

The 8761 is a low voltage, low skew PCI / PCI-X Clock Generator. The 8761 has a selectable REF_CLK or crystal input. The REF_CLK input accepts LVCMOS or LVTTL input levels. The 8761 has a fully integrated PLL along with frequency configurable clock and feedback outputs for multiplying and regenerating clocks with "zero delay". Using a 20MHz or 25MHz crystal or a 33.333MHz or 66.666MHz reference frequency, the 8761 will generate output frequencies of 33.333MHz, 66.666MHz, 100MHz and 133.333MHz simultaneously. The low impedance LVCMOS/LVTTL outputs of the 8761 are designed to drive 50Ω series or parallel terminated transmission lines.

当前筛选条件