封装信息

| CAD 模型: | View CAD Model |

| Pkg. Type: | TSSOP |

| Pkg. Code: | PGG20 |

| Lead Count (#): | 20 |

| Pkg. Dimensions (mm): | 6.5 x 4.4 x 1.0 |

| Pitch (mm): | 0.65 |

环境和出口类别

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

| Moisture Sensitivity Level (MSL) | 1 |

产品属性

| Pkg. Type | TSSOP |

| Lead Count (#) | 20 |

| Pb (Lead) Free | Yes |

| Carrier Type | Tube |

| Core Voltage (V) | 2.5V, 3.3V |

| Function | Buffer, Multiplexer |

| Input Freq (MHz) | 2000 |

| Input Type | HSTL, LVPECL |

| Inputs (#) | 2 |

| Length (mm) | 6.5 |

| MOQ | 148 |

| Moisture Sensitivity Level (MSL) | 1 |

| Output Banks (#) | 1 |

| Output Freq Range (MHz) | 2000 |

| Output Skew (ps) | 45 |

| Output Type | LVPECL |

| Output Voltage (V) | 2.5V, 3.3V |

| Outputs (#) | 5 |

| Package Area (mm²) | 28.6 |

| Pb Free Category | e3 Sn |

| Pitch (mm) | 0.65 |

| Pkg. Dimensions (mm) | 6.5 x 4.4 x 1.0 |

| Qty. per Carrier (#) | 74 |

| Qty. per Reel (#) | 0 |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Tape & Reel | No |

| Temp. Range (°C) | 0 to 70°C |

| Thickness (mm) | 1 |

| Width (mm) | 4.4 |

有关 MC100ES6014 的资源

描述

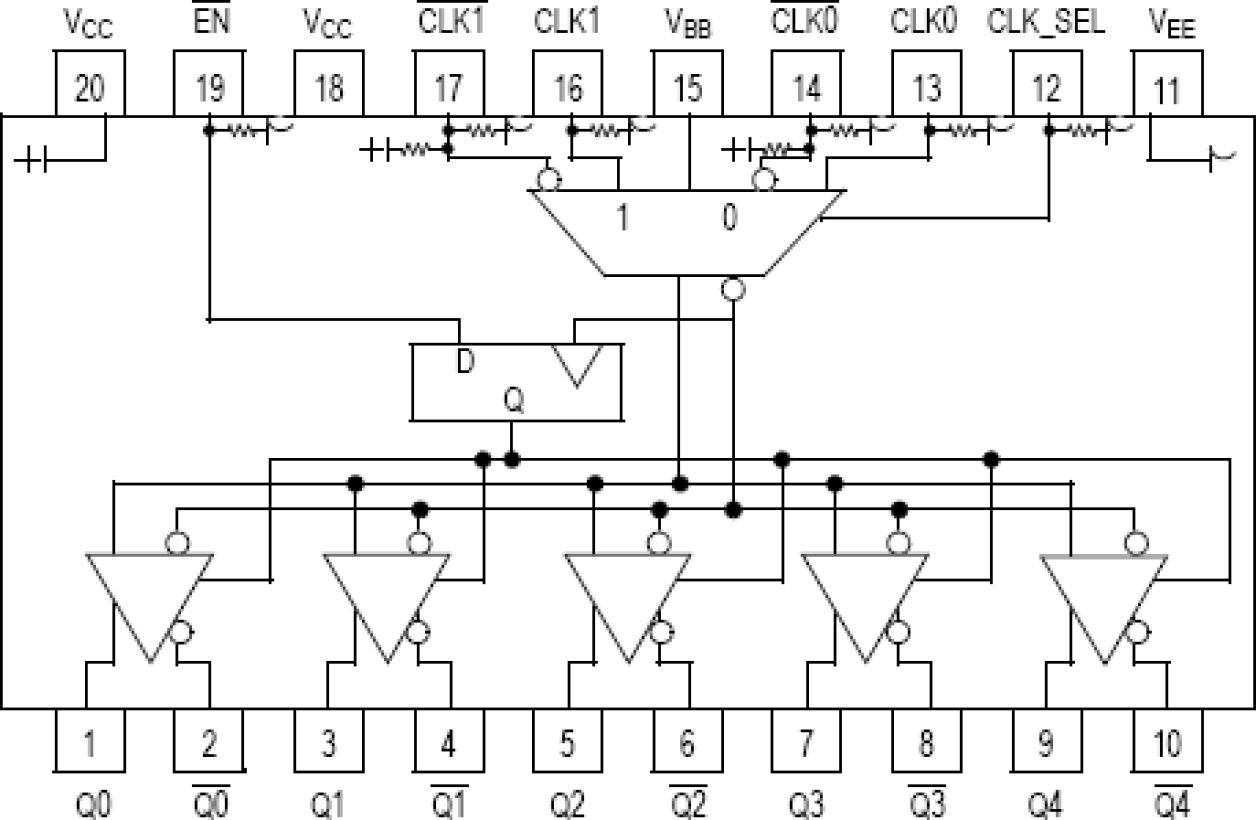

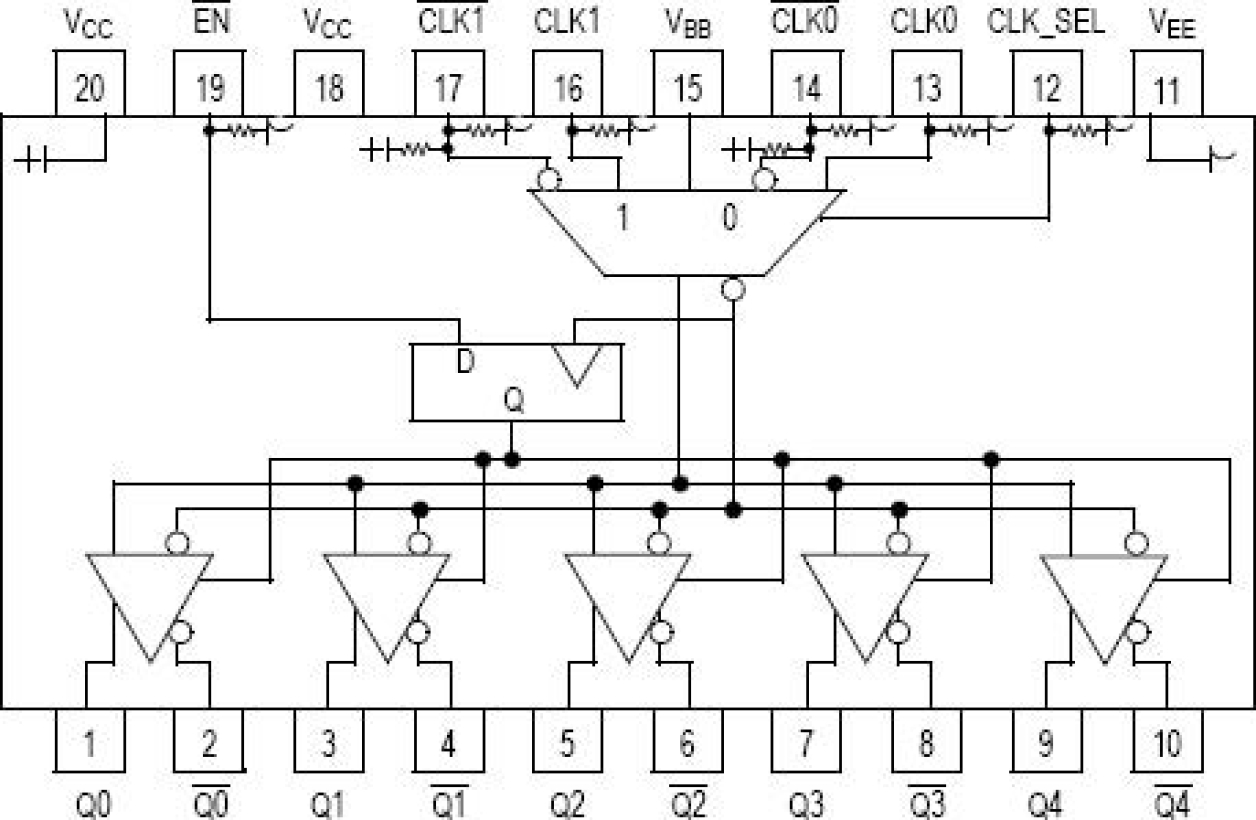

The MC100ES6014 is a low skew 1-to-5 differential driver, designed with clock distribution in mind, accepting two clock sources into an input multiplexer. The ECL/PECL input signals can be either differential or single-ended (if the VBB output is used). HSTL and LVDS inputs can be used when the ES6014 is operating under PECL conditions. The ES6014 specifically guarantees low output-to-output skew. Optimal design, layout, and processing minimize skew within a device and from device to device. To ensure that the tight skew specification is realized, both sides of any differential output need to be terminated identically into 50 ? even if only one output is being used. If an output pair is unused, both outputs may be left open (unterminated) without affecting skew. The common enable (EN) is synchronous, outputs are enabled/disabled in the LOW state. This avoids a runt clock pulse when the device is enabled/disabled as can happen with an asynchronous control. The internal flip flop is clocked on the falling edge of the input clock; therefore, all associated specification limits are referenced to the negative edge of the clock input. The MC100ES6014, as with most other ECL devices, can be operated from a positive VCC supply in PECL mode. This allows the ES6014 to be used for high performance clock distribution in +3.3 V or +2.5 V systems. Single ended CLK input pin operation is limited to a VCC ? 3.0 V in PECL mode, or VEE ? –3.0 V in ECL mode. Designers can take advantage of the ES6014's performance to distribute low skew clocks across the backplane or the board.