封装信息

| CAD 模型: | View CAD Model |

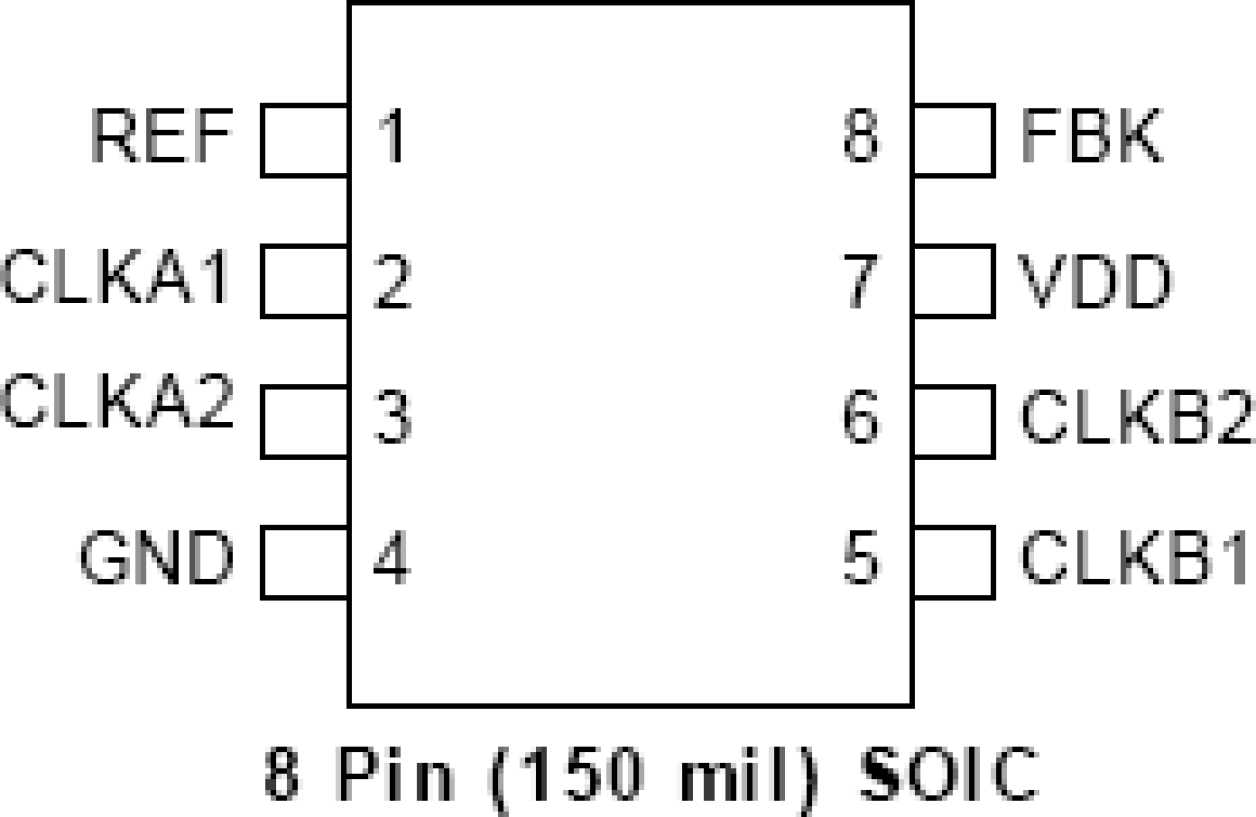

| Pkg. Type: | SOIC |

| Pkg. Code: | DCG8 |

| Lead Count (#): | 8 |

| Pkg. Dimensions (mm): | 4.9 x 3.9 x 1.5 |

| Pitch (mm): | 1.27 |

环境和出口类别

| Moisture Sensitivity Level (MSL) | 1 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

产品属性

| Lead Count (#) | 8 |

| Carrier Type | Tube |

| Moisture Sensitivity Level (MSL) | 1 |

| Qty. per Reel (#) | 0 |

| Qty. per Carrier (#) | 97 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range (°C) | -40 to 85°C |

| Advanced Features | Feedback Input, Spread Spectrum |

| C-C Jitter Max P-P (ps) | 375 |

| Core Voltage (V) | 3.3 |

| Feedback Input | Yes |

| Input Freq (MHz) | 10 - 133 |

| Input Type | LVCMOS |

| Inputs (#) | 1 |

| Length (mm) | 4.9 |

| MOQ | 194 |

| Output Banks (#) | 2 |

| Output Freq Range (MHz) | 10 - 133 |

| Output Skew (ps) | 200 |

| Output Type | LVCMOS |

| Output Voltage (V) | 3.3 |

| Outputs (#) | 4 |

| Package Area (mm²) | 19.1 |

| Pitch (mm) | 1.27 |

| Pkg. Dimensions (mm) | 4.9 x 3.9 x 1.5 |

| Pkg. Type | SOIC |

| Product Category | Zero Delay Buffers |

| Prog. Clock | No |

| Reference Output | No |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Spread Spectrum | Yes |

| Tape & Reel | No |

| Thickness (mm) | 1.5 |

| Width (mm) | 3.9 |

| 已发布 | No |

有关 MK2304-2 的资源

描述

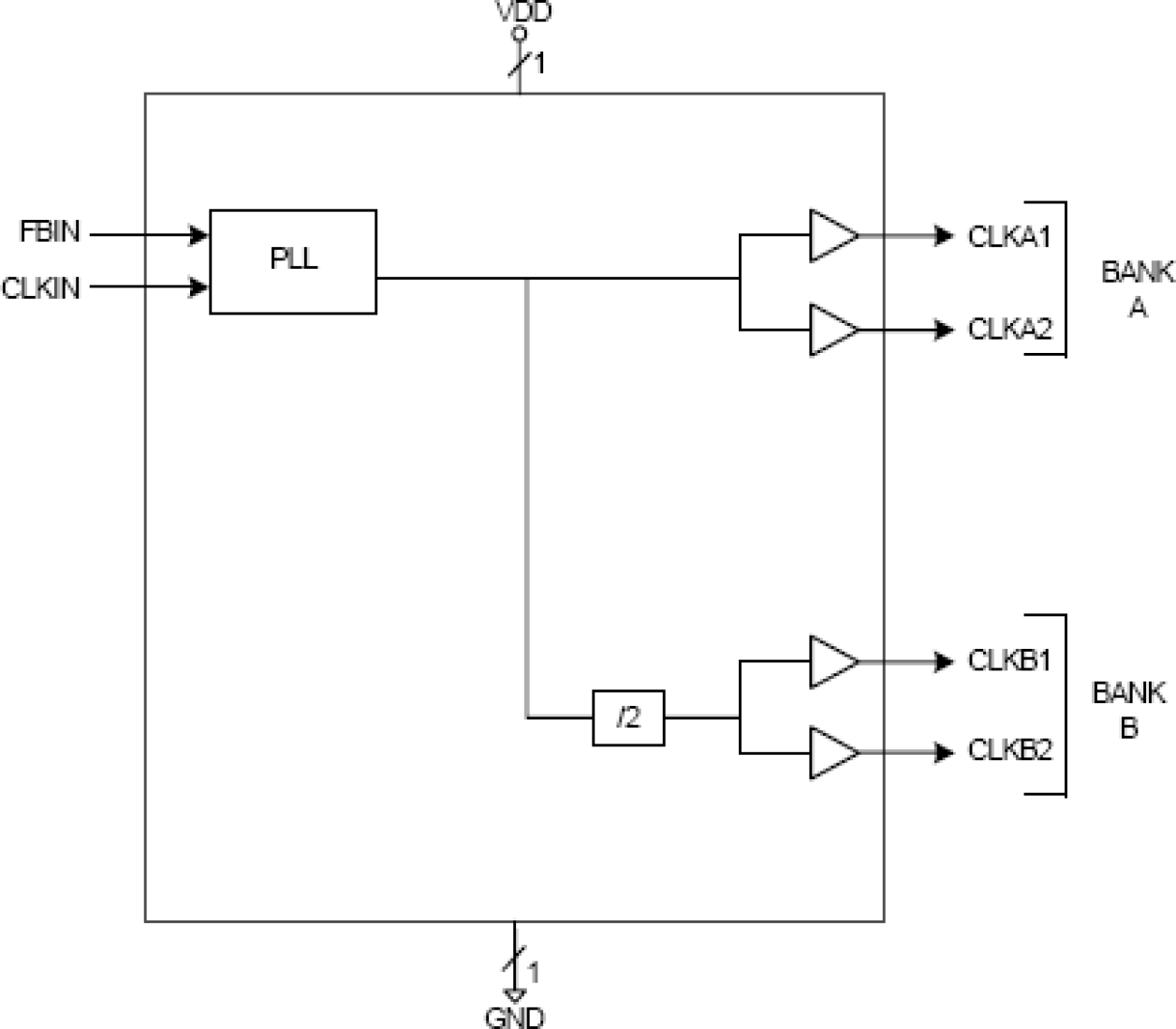

The MK2304-2 is a low jitter, low skew, high performance Phase Lock Loop (PLL) based zero delay buffer for high speed applications. Based on IDT's proprietary low jitter PLL techniques, the device provides four low skew outputs at speeds up to 133 MHz at 3.3 V. The MK2304-2 includes a bank of two outputs running at 1/2X. In the zero delay mode, the rising edge of the input clock is aligned with the rising edges of all 4 outputs. Compared to competitive CMOS devices, the MK2304-2 has the lowest jitter. The MK2304-2 PLL enters a power-down state when there are no rising edges on the REF input. In this mode, all outputs are tri-stated and the PLL is turned off, resulting in leass than 25 ?A of current draw. IDT manufactures the largest variety of clock generators and buffers and is the largest clock supplier in the world.