特性

- JEDEC Center Power / GND pinout for reduced noise.

- Equal access and cycle times

- – Commercial and Industrial: 10/12/15ns

- One Chip Select plus one Output Enable pin

- Bidirectional data inputs and outputs directly

- LVTTL-compatible

- Low power consumption via chip deselect

- Upper and Lower Byte Enable Pins

- Single 3.3V power supply

- Available in 44-pin, 400 mil plastic SOJ, 44-pin, 400 mil TSOP Type II, and 48-pin BGA packages

描述

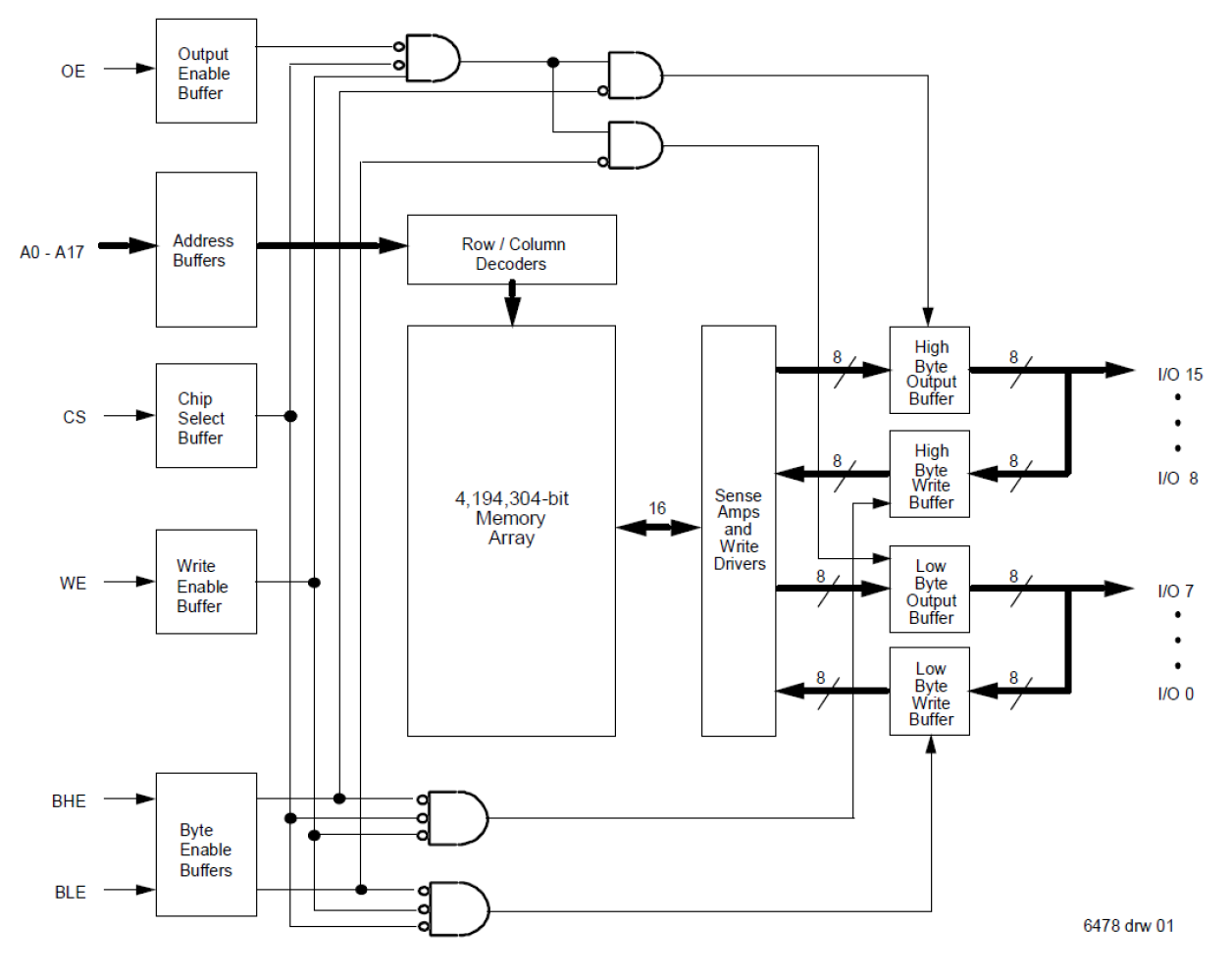

The 71V416 3.3V CMOS SRAM is organized as 256K x 16. All bidirectional inputs and outputs of the 71V416 are LVTTL-compatible and operation is from a single 3.3V supply. Fully static asynchronous circuitry is used, requiring no clocks or refresh for operation.

产品参数

| 属性 | 值 |

|---|---|

| Density (Kb) | 4096 |

| Bus Width (bits) | 16 |

| Core Voltage (V) | 3.3 |

| Organization | 256K x 16 |

| I/O Voltage (V) | 3.3 - 3.3 |

| Access Time (ns) | 10, 12, 15 |

| Temp. Range (°C) | -40 to 85°C, 0 to 70°C |

| Architecture | Asynchronous |

当前筛选条件