封装信息

| CAD 模型: | View CAD Model |

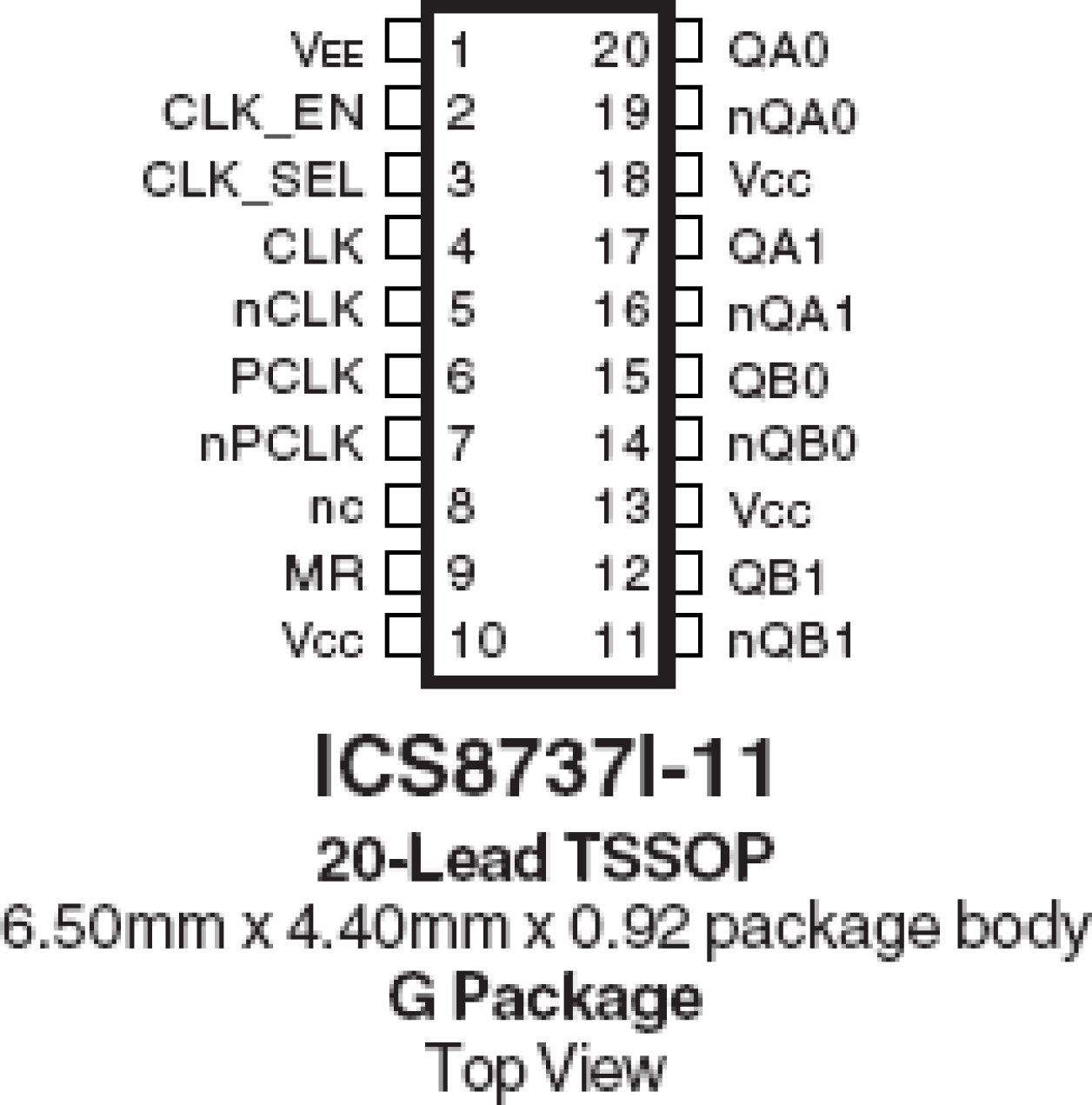

| Pkg. Type: | TSSOP |

| Pkg. Code: | PGG20 |

| Lead Count (#): | 20 |

| Pkg. Dimensions (mm): | 6.5 x 4.4 x 1.0 |

| Pitch (mm): | 0.65 |

环境和出口类别

| Moisture Sensitivity Level (MSL) | 1 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

产品属性

| Lead Count (#) | 20 |

| Carrier Type | Tube |

| Moisture Sensitivity Level (MSL) | 1 |

| Qty. per Reel (#) | 0 |

| Qty. per Carrier (#) | 74 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range (°C) | -40 to 85°C |

| Core Voltage (V) | 3.3 |

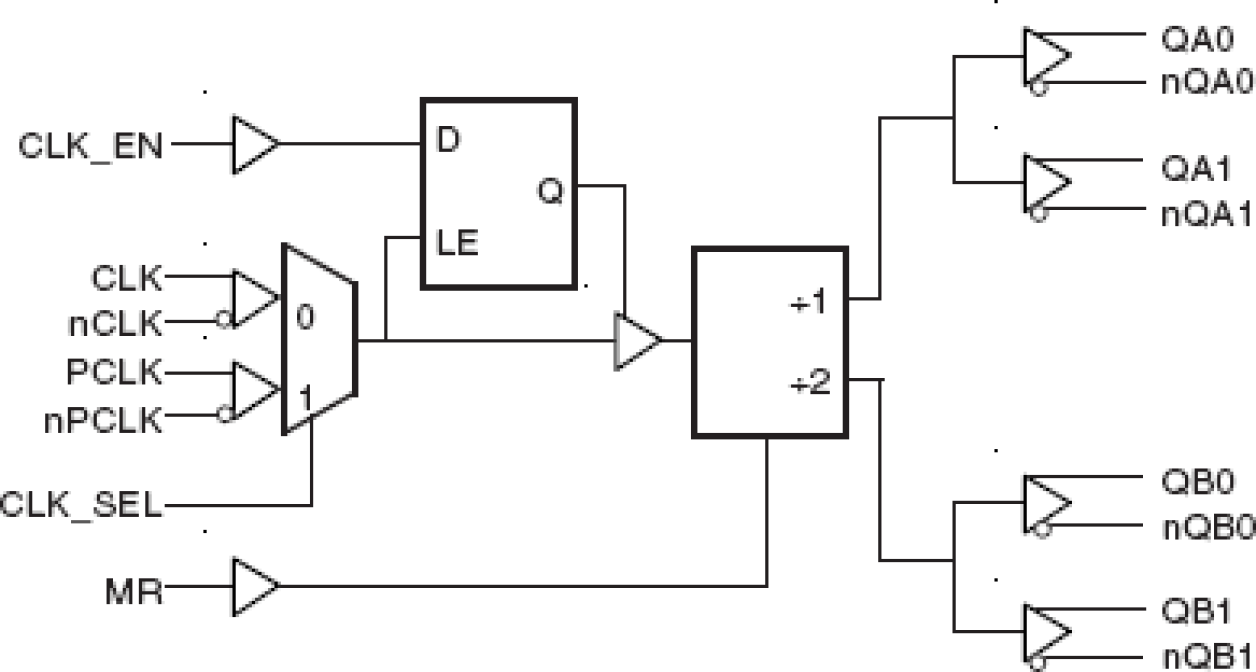

| Divider Value | 1, 2 |

| Function | Buffer, Multiplexer, Divider |

| Input Freq (MHz) | 650 |

| Input Type | CML, HCSL, HSTL, LVDS, LVPECL, SSTL |

| Inputs (#) | 2 |

| Length (mm) | 6.5 |

| MOQ | 74 |

| Output Banks (#) | 2 |

| Output Freq Range (MHz) | 650 |

| Output Skew (ps) | 75 |

| Output Type | LVPECL |

| Output Voltage (V) | 3.3 |

| Outputs (#) | 4 |

| Package Area (mm²) | 28.6 |

| Pitch (mm) | 0.65 |

| Pkg. Dimensions (mm) | 6.5 x 4.4 x 1.0 |

| Pkg. Type | TSSOP |

| Product Category | Clock Buffers & Drivers, Clock Dividers, Clock Multiplexers |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Tape & Reel | No |

| Thickness (mm) | 1 |

| Width (mm) | 4.4 |

有关 8737I-11 的资源

描述

The 8737I-11 is a low skew, high performance Differential-to-3.3V LVPECL Clock Generator/Divider. The 8737I-11 has two selectable clock inputs. The CLK, nCLK pair can accept most standard differential input levels. The PCLK, nPCLK pair can accept LVPECL, CML, or SSTL input levels. The clock enable is internally synchronized to eliminate runt pulses on the outputs during asynchronous assertion/deassertion of the clock enable pin. Guaranteed output and part-to-part skew characteristics make the 8737I-11 ideal for clock distribution applications demanding well defined performance and repeatability.