特性

- 逻辑和混合信号电路

- 高度灵活的宏单元

- 回读保护(Read Lock)

- 1.8V (±5%) 至 5V (±10%) VDD

- 1.8V(±5%)至 5V(±10%)VDD2(VDD2 ≤ VDD)

- 工作温度范围:-40°C 至 85°C

- 符合 RoHS 标准/无卤素

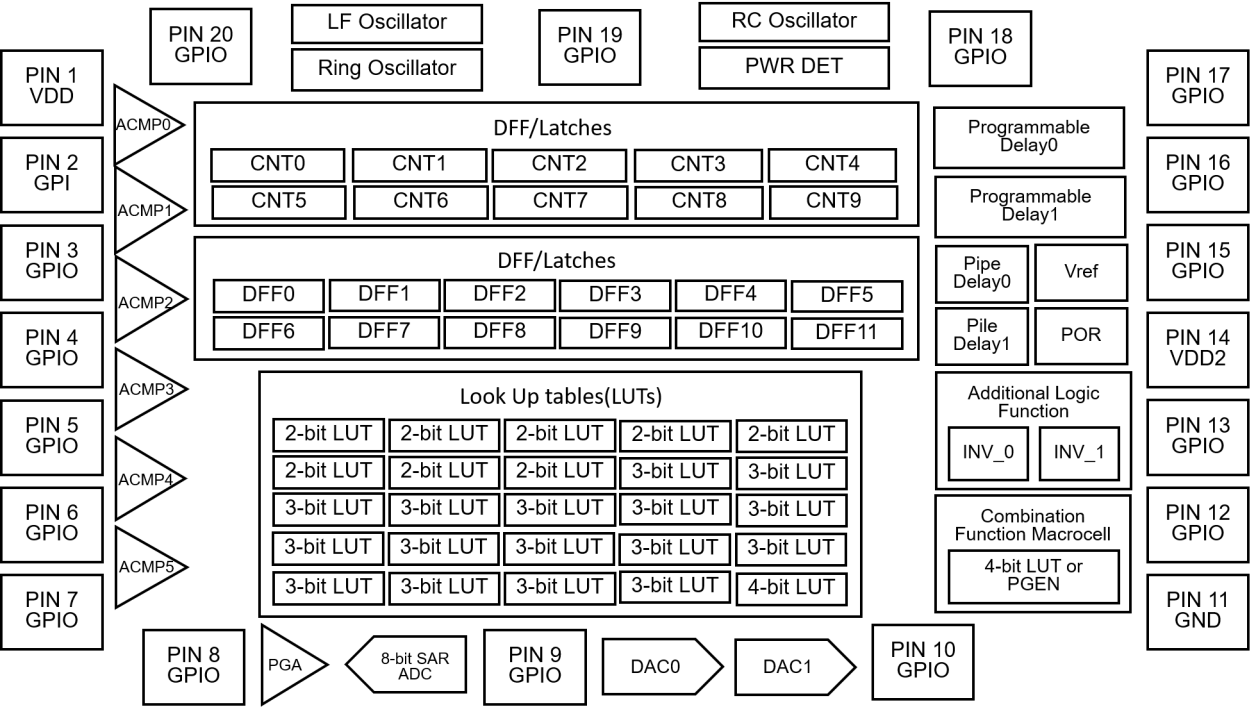

- 宏单元总览

- 8 位逐次逼近寄存器模数转换器 (SAR ADC)

- ADC 3 位可编程增益放大器 (PGA)

- 2 个数模转换器 (DAC)

- 6 个模拟比较器 (ACMP)

- 两个电压基准 (Vref)

- 25 个组合查找表 (LUT)

- 8 个 2 位 LUT

- 16 个 3 位 LUT

- 1 个 4 位 LUT

- 1 个组合功能宏单元

- 模式发生器或 4 位 LUT

- 3 个数字比较器/脉宽调制器 (DCMP/PWM),具有可选的死区

- 10 个计数器/延迟 (CNT/DLY)

- 2 个 14 位延迟/计数器

- 1 个 14 位延迟/计数器(唤醒睡眠控制)

- 1 个 14 位延迟/计数器/有限状态机

- 5 个 8 位延迟/计数器

- 1 个 8 位延迟/计数器/有限状态机

- 12 个 D 触发器/锁存器

- 2 个管道延迟 – 16 级/2 路输出

- 2 个带隙

- 2 个具有边缘检测的可编程延迟

- 3 个内部振荡器

- 低频

- 指环

- RC 25kHz 和 2MHz

- 上电复位 (POR)

- 从 SPI

描述

SLG46621 提供一个小型低功耗组件来实现常用的混合信号功能。 用户通过对一次性可编程 (OTP) 非易失性存储器 (NVM) 进行编程来配置 SLG46621 的互连逻辑、IO 引脚和宏单元,从而进行电路设计。 这款高灵活性的器件能在超小尺寸、超低功耗的单个集成电路中实现丰富多样的混合信号功能设计。 SLG46621 上的附加电源 (VDD2) 能够在同一设计中连接两个独立的电压域。 用户可将每个电源的专用引脚配置为 VDD 和 VDD2 电压域的输入、输出或输入和输出(由内部逻辑动态控制)。 设计人员可利用现有的宏单元来实现混合信号功能,将两个电压域以高到低和低到高的方向进行简单的直通式电平转换。

此为出厂可配置设备。

试用自定义部件配置工具。

试用自定义部件配置工具。

产品参数

| 属性 | 值 |

|---|---|

| Nominal VDD | 1.71 - 5.5 |

| VDD2 (V) | 1.71 - 5.5 |

| GPIOs (#) | 17 |

| Special Features | 2x DAC, 3x PWM, ADC (8-bit SAR) |

| ACMP Channels (#) | 6 |

| DCMP | 3 |

| CNT/DLY (Max) (#) | 10 |

| LUTs (Max) (#) | 26 |

| D Flip-flops (DFFs) (#) | 12 |

| Pipe Delay | 2x 16-stage |

| # of Programable Delays (#) | 2 |

| Oscillator Type | RC OSC, LF OSC, Ring OSC |

| Interface | SPI |

| Memory Type | OTP |

| Temp. Range (°C) | -40 to +85°C |

封装选项

| Pkg. Type | Pkg. Dimensions (mm) | Lead Count (#) | Pitch (mm) |

|---|---|---|---|

| TQFN | 2.0 x 3.0 | 20 | 0.4 |

应用

- 个人计算机和服务器

- 电脑周边设备

- 消费电子

- 数据通信设备

- 手持式和便携式电子产品