NEW

封装信息

| CAD 模型: | View CAD Model |

| Pkg. Type: | TQFN |

| Pkg. Code: | |

| Lead Count (#): | 20 |

| Pkg. Dimensions (mm): | 2.0 x 3.0 |

| Pitch (mm): | 0.4 |

环境和出口类别

| Pb (Lead) Free | Yes |

| Moisture Sensitivity Level (MSL) | 1 |

| ECCN (US) | |

| HTS (US) |

产品属性

| Pkg. Type | TQFN |

| Lead Count (#) | 20 |

| Carrier Type | Tape & Reel |

| Pb (Lead) Free | Yes |

| Temp. Range (°C) | -40 to +85°C |

| Country of Assembly | TAIWAN |

| Country of Wafer Fabrication | TAIWAN |

| ACMP Channels (#) | 1 |

| Additional Features | Supported in Go Configure™ Software Hub |

| CNT/DLY (Max) (#) | 3 |

| DCMP | - |

| DFF (Max) (#) | 10 |

| GPIOs (#) | 10 |

| Interface | I2C |

| LUTs (Max) (#) | 12 |

| MOQ | 3000 |

| Memory Type | OTP |

| Moisture Sensitivity Level (MSL) | 1 |

| Nominal VDD | 2.3 - 5.5 |

| Oscillator Type | LF OSC, Ring OSC |

| Pattern Generator | 1 |

| Peak Output Current IPK (A) | 2 |

| Pipe Delay | 16-stage |

| Pitch (mm) | 0.4 |

| Pkg. Dimensions (mm) | 2.0 x 3.0 |

| Qty. per Reel (#) | 3000 |

| Special Features | 1x H-/2x Half-Bridge, PWM, CCMP |

| VDD2 (V) | 3 - 13.2 |

有关 SLG47104 的资源

描述

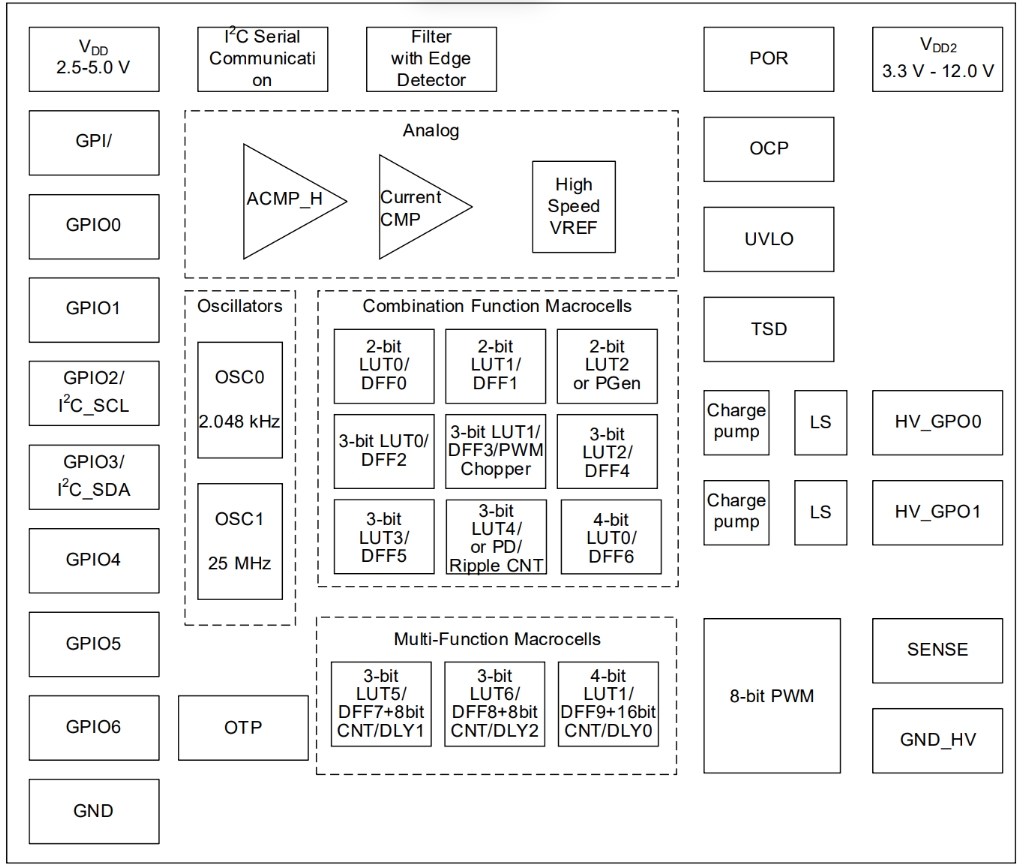

SLG47104 为常用的混合信号和桥接功能提供了一个小型、低功耗的元件。 用户通过对一次性可编程 (OTP) 非易失性存储器 (NVM) 进行编程来配置 SLG47104 的互连逻辑、IO 引脚、高压引脚和宏单元,从而创建电路设计。 可配置的 PWM 宏单元与特殊的高压输出相结合,可用于电机驱动或负载驱动应用。 采用高压引脚,支持用户设计智能电平转换器或驱动高压大电流负载。