特性

- 2 个电源输入:

- 2.5V (±8%) 至 5.0V (±10%)VDD

- 3.3V (±9%) 至 12.0V (±10%) VDD2

- 4 个高压大电流驱动 GPO

- 双/单全桥驱动器选项

- 四/双/单半桥驱动器选项

- 压摆率模式:

- 电机驱动模式

- 预驱动器(MOSFET 驱动器)模式

- 睡眠功能

- 低 RDS(ON) 高边 + 低边电阻 = 0.4Ω(典型值)

- 2A 峰值,每全桥 1.5A RMS(VDD2 = 5V,TA = 25°C)

- 4A 峰值,每两个并联的全桥 3A RMS(VDD2 = 5V,TA = 25°C)

- 2A 峰值,每半桥 GPO 1.5A RMS(VDD2 = 5V,TA = 25°C)

- 集成过流 (OCP)、短路、欠压锁定 (UVLO)、热关断 (TSD) 保护

- SENSE_A、SENSE_B 输入端连接到电流比较器以进行电流控制

- 故障信号指示灯(OCP/UVLO/TSD)

- 差分放大器,带积分器和比较器,用于电机速度控制功能

- 2 个电流检测比较器,带动态 Vref 模式

- 2 个高速通用 ACMP

- 模式:UVLO、OCP、TSD、电压监控器、电流监控器

- 1 个基准电压源 (Vref) 输出

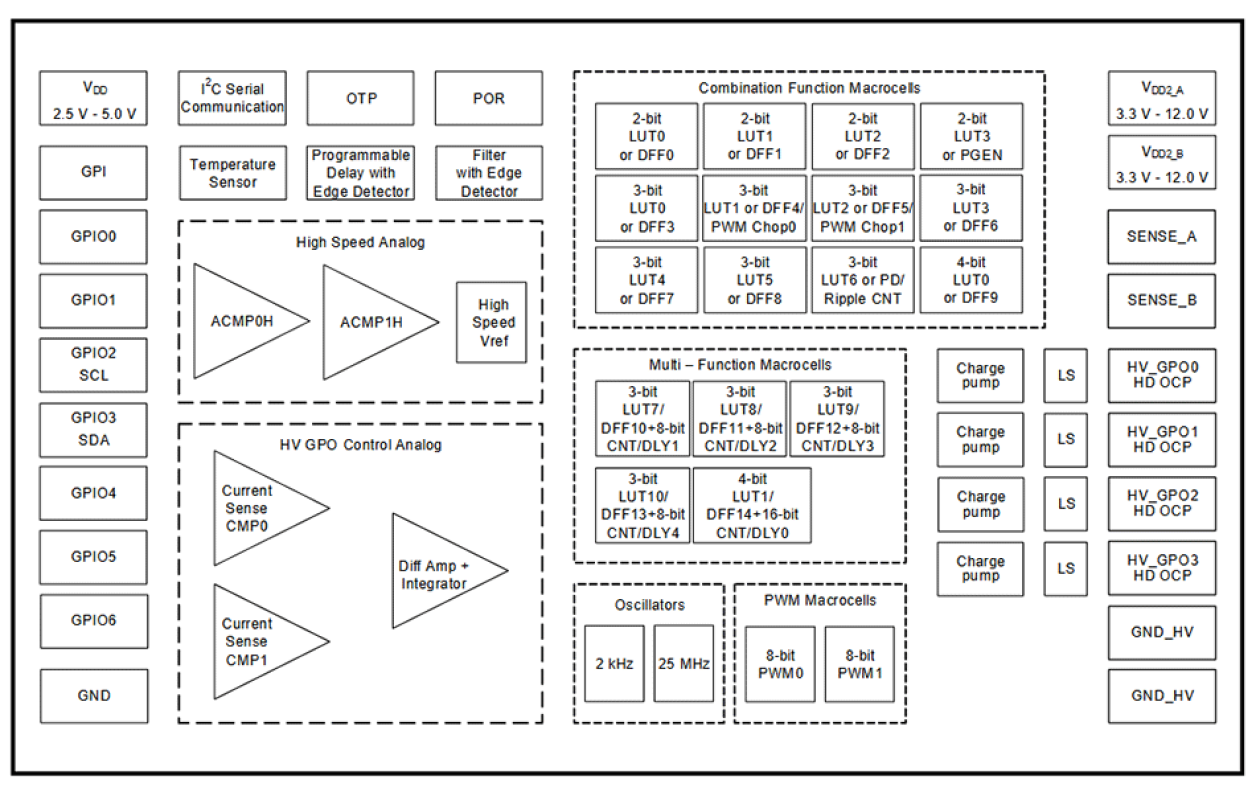

- 5 个多功能宏单元

- 4 个可选 DFF/LATCH/3 位 LUT + 8 位延迟/计数器

- 1 个可选 DFF/LATCH/4 位 LUT + 16 位延迟/计数器

- 12 个组合功能宏单元

- 3 个可选 DFF/LATCH 或 2 位 LUT

- 1 个可选可编程码型发生器或 2 位 LUT

- 6 个可选 DFF/LATCH 或 3 位 LUT

- 1 个可选管道延迟或纹波计数器或 3 位 LUT

- 1 个可选 DFF/LATСH 或 4 位 LUT

- 2 个 PWM 宏单元

- 灵活的 8 位/7 位 PWM 模式,具有占空比控制

- 16 个预设占空比寄存器开关模式,用于 PWM、正弦波或其他波形

- 串行通信

- I2C 协议接口

- 具有边缘检测器输出的可编程延迟

- 附加逻辑功能: 一个带边缘检测器的去毛刺滤波器

- 2 个振荡器 (OSC)

- 2.048 kHz 振荡器

- 25 MHz 振荡器

- 带 ACMP 连接输出的模拟温度传感器

- 上电复位(POR)

- 一次性可编程存储器

- 工作温度范围:-40°C 至 105°C

- 符合 RoHS 标准/无卤素

- 20 引脚 STQFN 封装:2mm x 3mm x 0.55mm,0.4mm 间距

描述

SLG47105-EV 为常用的混合信号和桥接功能提供了一个小型、低功耗的元件。 用户通过对一次性可编程 (OTP) 非易失性存储器 (NVM) 进行编程来配置 SLG47105-EV 的互连逻辑、IO 引脚、高压引脚和宏单元,从而创建电路设计。 可配置的 PWM 宏单元与特殊的高压输出相结合,可用于电机驱动或负载驱动应用。 高压引脚允许设计智能电平转换器或驱动高压大电流负载。

产品参数

| 属性 | 值 |

|---|---|

| Nominal VDD | 2.3 - 5.5 |

| VDD2 (V) | 3 - 13.2 |

| GPIOs (#) | 12 |

| Special Features | 2x CCMP, 2x H-/4x Half-Bridge, 2x PWM, Int&Diff Amp |

| ACMP Channels (#) | 2 |

| CNT/DLY (Max) (#) | 5 |

| Look-up Table (LUTs) | 17 |

| D Flip-flops (DFFs) (#) | 15 |

| Pipe Delay | 16-stage |

| # of Programable Delays (#) | 1 |

| Oscillator Type | LF OSC, Ring OSC |

| Temperature Sensor (ch) (#) | 1 |

| Temp. Range (°C) | -40 to +105°C |

| Interface | I2C |

| Memory Type | OTP |

封装选项

| Pkg. Type | Pkg. Dimensions (mm) | Lead Count (#) | Pitch (mm) |

|---|---|---|---|

| TQFN | 2.0 x 3.0 | 20 | 0.4 |

应用

- 户外电子产品

- 工厂自动化

- 电动自行车

- 电力电子

- 电动汽车充电站

- 个人计算机和服务器

- 电机驱动器

- 高压 MOSFET 驱动器

- LED 矩阵调光器

当前筛选条件