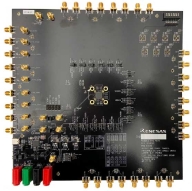

概览

描述

固定外形交换机,通常称为“披萨盒”或“堆叠式”交换机,与发展缓慢的传统机箱型号相比,它具有引人注目的优势。 可堆叠设计可扩展成本效益,降低购置、技术支持和电力的成本,从而降低总拥有成本(TCO)。 这种设计优先考虑精确时序、集成性和灵活性,使网络和系统开发人员能够满足超过 400GHz 的 112G PAM4 的苛刻要求。

系统优势:

- 高度集成的定时源,无需额外的时钟器件

- 允许 <100fs RMS 输出,以支持 112Gbps SerDes 互连时钟

- 支持同步以太网(SyncE)、JESD204B/C 和 IEEE 1588 G.8262.1 和 G.8262 电信边界时钟要求以及 G.8273.2 C/D 类时间精度

产品对比

应用

远程测试该板卡

该板卡已上线云上实验室(Lab on the Cloud),使用我们的 PC 图形界面,无需实体板卡,便可在虚拟实验室中立即开始配置和测试设计。

LDO

产品

LDO

产品

LDO

产品

LDO

产品

LDO

产品

LDO

产品

System Synchronizer

产品

FemtoClock Low Jitter Clock Generator

产品

Fanout Buffer

产品

Exiting Interactive Block Diagram