USB 2.0 高速/全速 PHY

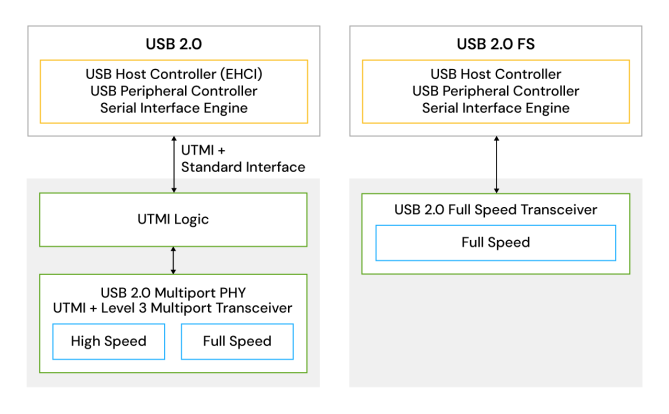

通过将 USB 2.0 PHY 与 UTMI 逻辑相结合,我们提供了一种符合标准接口规范(UTMI+ 3 级)的接口解决方案。 此外,USB 2.0 FS 收发器经过专门的架构设计,将 USB 全速/低速的 I/O 缓冲器与 USB 2.0 PHY 分离,从而实现了占地面积更小的紧凑型 USB 2.0 FS 解决方案。

瑞萨电子接口 IP 包括 PCIe/USB/SATA PHY、USB LINK、PCI Express LINK、SATA LINK、MIPI、FPD_Link、CAN、以太网 AVB 以及以太网 TSN,经过我们的微控制器和微计算机验证,均具备可靠的性能。

以下部分 IP 已签订设计合作。 请联系我们了解详情。

| 功能 | IP 名称 | 进程(或软宏) | 状态 | 文档 | 查询 |

|---|---|---|---|---|---|

| USB LINK | USB 3.1 (Gen1) xHCI 主机控制器 | 软宏 | 初步 (需咨询) | 联系我们 | |

| USB 3.1 (Gen1) 外围控制器 | 软宏 | 初步 (需咨询) | |||

| USB 2.0 EHCI 主机控制器 | 软宏 | 可提供 | |||

| USB 2.0 外围控制器 | 软宏 | 可提供 | |||

| USB 2.0 On-The-Go (OTG) 控制器 | 软宏 | 可提供 | |||

| PCI Express LINK 配置工具 | 可配置 PCI Express 4.0 链路控制器 | 软宏 | 初步 (需咨询) | 联系我们 | |

| PCI Express 5.0 链路控制器 | 软宏 | 可提供 | |||

| CAN | CAN 控制器 | 软宏 | 初步 (需咨询) | 联系我们 | |

| CAN FD | CAN FD 多通道型控制器 | 软宏 | 初步 (需咨询) | 联系我们 | |

| CAN FD 单通道型控制器 | 软宏 | 可提供 | |||

| 以太网 AVB | 以太网 AVB 终端站 | 软宏 | 初步 (需咨询) | 联系我们 | |

| 以太网 TSN | 以太网 TSN 终端站 | 软宏 | 初步 (需咨询) | 应用示例 | 联系我们 |

| 以太网 TSN 2 层/ 3 层交换机 | 软宏 | 初步 (需咨询) | 应用示例 | ||

| FPD-Link | FPD-Link RX | TSMC 28nm | 可提供 | 联系我们 | |

| FPD-Link RX | TSMC 22nm | 可提供 | |||

| FPD-Link TX | TSMC 28nm | 可提供 | |||

| FPD-Link TX | TSMC 22nm | 可提供 | |||

| LVDS | LVDS IO 缓冲器 | TSMC 7, 12, 16, 22, 28, 40nm & Samsung 14nm | 可提供 | 联系我们 | |

| PCIe/USB/SATA PHY | SerDes PHY 高达 5Gbps PCIe2.1,USB 3.0 SS | TSMC 28nm | 可提供 | 联系我们 | |

| USB2.0 PHY:多端口收发器 配备 UTMI+ 3 级接口 | TSMC 28nm | 可提供 | |||

| USB2.0 PHY:多端口收发器 配备 UTMI+ 3 级接口 | Samsung 28nm | 可提供 | |||

| USB2.0 PHY:单端口收发器 配备 UTMI+ 3 级接口 | TSMC 40nm | 可提供 | |||

| USB2.0 PHY:单端口收发器 配备 UTMI+ 3 级接口 | TSMC 22nm | 可提供 | |||

| USB 2.0 全速(FS)收发器 | TSMC 22nm | 可提供 | |||

| MIPI D-PHY | MIPI D-PHY:配备 FPD-Link TX 的 DSI 发射器 | 软宏与 TSMC 22nm | 可提供 | 联系我们 | |

| MIPI D-PHY:CSI-2 接收器 | 软宏与 TSMC 22nm | 可提供 | |||

| MIPI D-PHY:CSI-2/DSI 收发器 | 软宏与 TSMC 40nm | 可提供 | |||

| MIPI D-PHY:CSI-2/DSI 收发器 | 软宏与 Samsung 28nm | 可提供 | |||

| MIPI D-PHY:CSI-2/DSI 收发器 | 软宏与 TSMC 22nm | 可提供 | |||

| MIPI D-PHY(控制器) | MIPI CSI-2 接收器 IP 核 | 软宏 | 初步 (需咨询) | 联系我们 | |

| MIPI DSI-2 发射器 IP 核 | 软宏 | 初步 (需咨询) |

通过将 USB 2.0 PHY 与 UTMI 逻辑相结合,我们提供了一种符合标准接口规范(UTMI+ 3 级)的接口解决方案。 此外,USB 2.0 FS 收发器经过专门的架构设计,将 USB 全速/低速的 I/O 缓冲器与 USB 2.0 PHY 分离,从而实现了占地面积更小的紧凑型 USB 2.0 FS 解决方案。

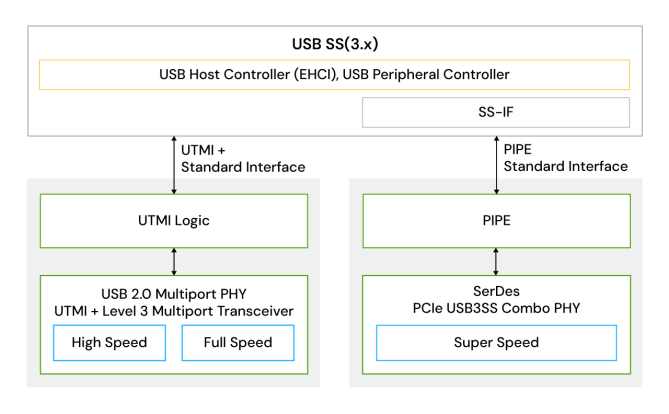

通过集成用于 USB SuperSpeed 的 SerDes IP 与 PIPE 逻辑并结合 USB 2.0 PHY 和 UTMI 逻辑,我们提供了符合标准接口规范(PIPE 接口和 UTMI+ 3 级)的接口解决方案。

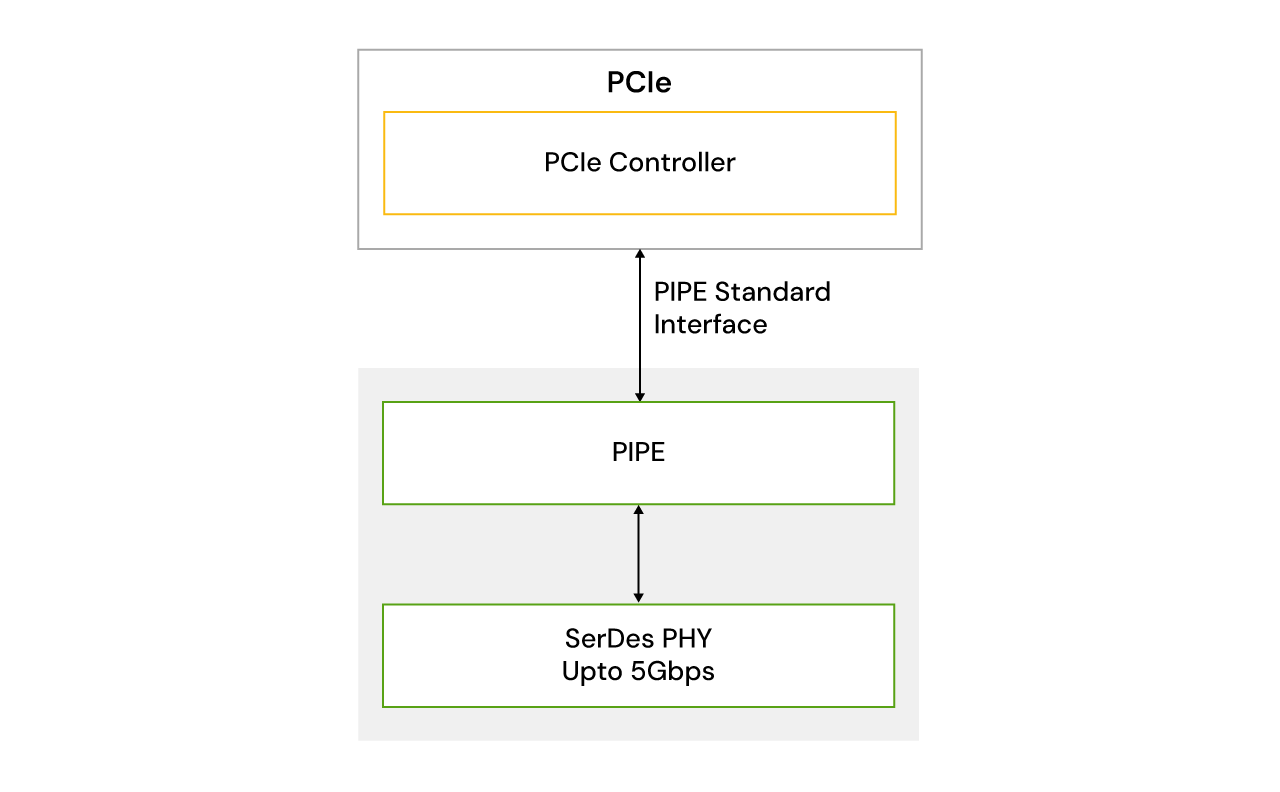

通过将 SerDes IP 与 PIPE 逻辑相结合,我们提供了符合 PCIe 标准规范的接口解决方案。

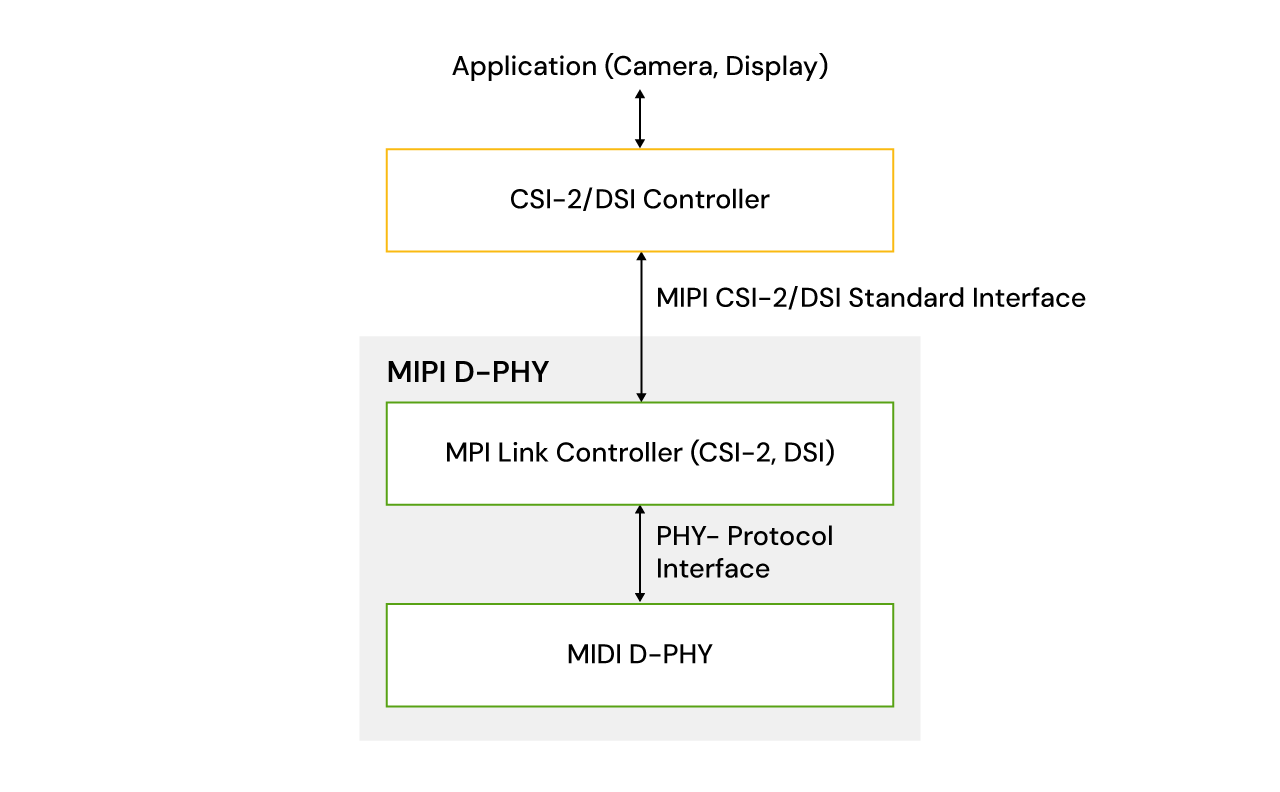

MIPI D-PHY 是一种专为高速串行通信设计的物理层接口标准,主要应用于摄像头(CSI-2)和显示器(DSI)领域。 该标准可实现 CPU、图形引擎与系统内存等组件之间的低功耗、高带宽数据传输。 通过结合 MIPI 控制器 IP,MIPI D-PHY IP 可提供符合 MIPI CSI-2(摄像头串行接口 2)及 DSI(显示串行接口)标准的完整接口解决方案。